### **University of South Carolina** Scholar Commons

Theses and Dissertations

2015

# Investigation of Modular Multilevel Converter Performance under Non-Ideal Distribution System **Conditions**

Rostan Rodrigues University of South Carolina

Follow this and additional works at: http://scholarcommons.sc.edu/etd

Part of the Electrical and Computer Engineering Commons

#### Recommended Citation

Rodrigues, R. (2015). Investigation of Modular Multilevel Converter Performance under Non-Ideal Distribution System Conditions. (Doctoral dissertation). Retrieved from http://scholarcommons.sc.edu/etd/3656

This Open Access Dissertation is brought to you for free and open access by Scholar Commons. It has been accepted for inclusion in Theses and Dissertations by an authorized administrator of Scholar Commons. For more information, please contact SCHOLARC@mailbox.sc.edu.

# INVESTIGATION OF MODULAR MULTILEVEL CONVERTER PERFORMANCE UNDER NON-IDEAL DISTRIBUTION SYSTEM CONDITIONS

by

Rostan Rodrigues

Bachelor of Engineering University of Mumbai, 2006

Master of Science California State University, Chico, 2010

Submitted in Partial Fulfillment of the Requirements

For the Degree of Doctor of Philosophy in

**Electrical Engineering**

College of Engineering and Computing

University of South Carolina

2015

Accepted by:

Herbert L. Ginn III, Major Professor

Roger A. Dougal, Committee Member

Charles Brice, Committee Member

Jun Li, Committee Member

Lacy Ford, Senior Vice Provost and Dean of Graduate Studies

© Copyright by Rostan Rodrigues, 2015

All Rights Reserved.

## **DEDICATION**

This dissertation is dedicated to my Family.

#### **ACKNOWLEDGEMENTS**

I would like to express my most sincere appreciations to my advisor, Dr. Herbert Ginn, for his professional and very valuable guidance over the course of my Ph.D. studies. Thanks for his encouragements and helps in both academic and personal life.

Many thanks to my Ph.D. committee members: Dr. Roger Dougal, Dr. Charles W. Brice and Dr. Jun Li for those invaluable discussions and timely feedback.

Thanks to the faculty and staff of the Electrical Engineering department for their continuous support: Rich Smart, Hope Johnson, Blake Langland, Nat Paterson, Ashley Burt and international student advisor Lauren Smith.

Many thanks to my colleagues Pietro Cairoli, Huaxi Zheng, Reza Dehnavi, Dan Li, Rod Leonard, Grant Conklin, Helder Paise who were always ready to help me in academic and personal life. Thanks to Dr. Guangda Chen for his valuable contribution in the lab.

I would like to acknowledge the support of GRAPES research center and ABB corporate research center, Raleigh for their sponsored fellowship, funding for hardware development, internship opportunity and valuable advice over the course of my dissertation.

#### **ABSTRACT**

The Modular Multilevel Converter (MMC) is an emerging power converter technology that has caught widespread attention mainly because of several technical and economic benefits such as modular realization, easy scalability, low total harmonic distortion, fail-safe operations etc. The MMC is comprised of a series connection of submodules (SM). A sub-module is made by either a half-bridge or a full-bridge IGBT device and a capacitor as a source of energy connected across the bridge. This modular structure allows for the possibility to design high-voltage converters handling hundreds of kilo-volts without direct series connection of the power semiconductor devices.

Due to its modular and safe-fail structure, ability to work at low switching frequency (few hundreds of Hz) and reduced filtering requirements the MMCs are suitable for utility applications. One of the main challenges of a utility MMC is operation under non-ideal grid supply conditions. This includes phase to phase faults, phase to ground faults, non-sinusoidal grid supply etc.

This dissertation presents a novel control strategy for MMC based on frequency domain decomposition of the converter currents. The converter supply voltage is also decomposed into symmetrical components. By using the positive sequence grid voltage component as a reference voltage the control system can produce symmetric sinusoidal phase currents under any type of grid unbalance condition. A novel circulating current

controller based on frequency domain decomposition of arm currents is also presented which minimizes DC bus current ripples during unbalance grid supply

A novel and simple method for estimating operating region of certain MMC parameters as a function of input variables (grid voltages and power references) is developed. The function of the operating region with respect to key system parameters ensures that the operating region can be maximized

Finally, a new simplified loss modeling technique and a power reference computation algorithm is developed in order to extend its operating limit under certain unbalance conditions. The presented control architecture with a simplified real-time loss modeling method assures the best possible performance of a MMC during non-ideal supply conditions.

# TABLE OF CONTENTS

| DEDICATION                                                                                              | iii  |

|---------------------------------------------------------------------------------------------------------|------|

| ACKNOWLEDGEMENTS                                                                                        | iv   |

| Abstract                                                                                                | V    |

| LIST OF TABLES                                                                                          | ix   |

| LIST OF FIGURES                                                                                         | X    |

| LIST OF ABBREVIATIONS                                                                                   | . XV |

| CHAPTER 1 INTRODUCTION                                                                                  | 1    |

| CHAPTER 2 MODELING AND TRADITIONAL CONTROL OF MODULAR MULTILEVEL CONVERTERS                             | 4    |

| 2.1 overview of Double-star configuration MMC                                                           | 4    |

| 2.2 MMC Modeling                                                                                        | 5    |

| 2.3 Selection of arm inductace and submodule capacitance                                                | . 11 |

| 2.4 MMC control structure                                                                               | . 13 |

| 2.5 Simulation verification of MMC system with designed controllers                                     | . 25 |

| CHAPTER 3 MODULAR MULTILEVEL CONVERTER WITH NON-IDEAL AC SUPPLY                                         | . 30 |

| 3.1 MMC performance under Non-ideal grid conditions                                                     | . 30 |

| 3.2 Previously Suggested Methods for MMC performance Improvement under supply asymmetry                 | . 36 |

| CHAPTER 4 ADVANCED CONTROL STRATEGY FOR MODULAR MULTILEVEL CONVERTERS UNDER NON-IDEAL SUPPLY CONDITIONS |      |

| 4.1 Current's Physical Component (CPC) power theory                                                     | . 38 |

| 4.2 CPC based Control structure design                                                                     | 45  |

|------------------------------------------------------------------------------------------------------------|-----|

| 4.3 Simulation Results                                                                                     | 53  |

| CHAPTER 5 ESTIMATION AND EXTENSION OF MODULAR MULTILEVEL CONVERTER OPERATING REGION UNDER UNBALANCE SUPPLY | 75  |

| 5.1 Developing average model for estimation of various MMC parameters                                      | 76  |

| 5.2 Extension of MMC operating region during non-ideal supply conditions                                   | 87  |

| CHAPTER 6 CONCLUSION AND FUTURE WORK                                                                       | 110 |

| References                                                                                                 | 113 |

| APPENDIX A DESIGN OF TRADITIONAL CONTROLLERS                                                               | 119 |

| A.1 Phase current controller design                                                                        | 119 |

| A.2 Power controller design                                                                                | 122 |

| A.3 Circulating current controller design                                                                  | 124 |

| APPENDIX B DESIGN OF CPC BASED MMC CONTROLLERS                                                             | 127 |

| B.1 phase current controller design                                                                        | 127 |

| B.2 circulating current control design                                                                     | 132 |

| APPENDIX C ESTIMATION OF IGBT AND DIODE PARAMETERS                                                         | 135 |

# LIST OF TABLES

| Table 2.1 Main Circuit Parameters and Operating Conditions of Simulated System    | 26 |

|-----------------------------------------------------------------------------------|----|

| Table 3.1 Symmetric component decomposition of unbalanced grid voltages test case | 31 |

| Table 5.1 Separating sub-module current into individual semiconductor currents    | 90 |

| Table 5.2 Semiconductor switching transitions                                     | 91 |

# LIST OF FIGURES

| Figure 1.1 Circuit configurations of MMC (a) Star configured MMC (b) Delta configured MMC(c) Double star Configured MMC (d) The Dual MMC                                            |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2.1 Half-bridge three-phase Modular Multilevel Converter                                                                                                                     | 5  |

| Figure 2.2 MMC with equivalent circuit of sub-modules                                                                                                                               | 7  |

| Figure 2.3 Circulating Current Transfer Function                                                                                                                                    | 11 |

| Figure 2.4 Complete control structure of a MMC                                                                                                                                      | 13 |

| Figure 2.5 PSC-PWM modulation scheme block diagram                                                                                                                                  | 15 |

| Figure 2.6 Six-level PSC-PWM with modulating signal                                                                                                                                 | 16 |

| Figure 2.7 Block diagram of Modulation and Voltage balancing scheme                                                                                                                 | 18 |

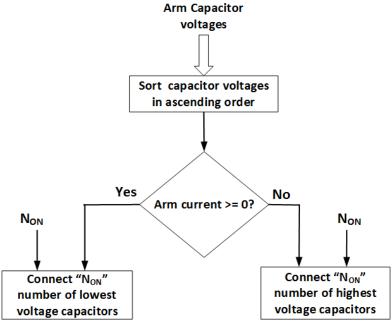

| Figure 2.8 Conventional Voltage Balancing Algorithm                                                                                                                                 | 18 |

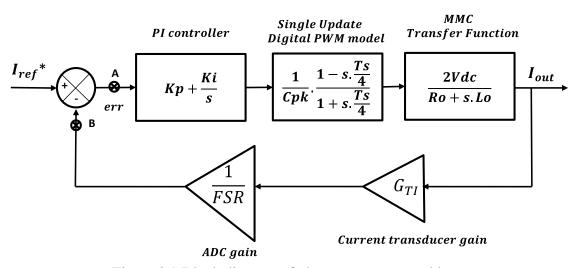

| Figure 2.9 Block diagram of phase current control loop                                                                                                                              | 21 |

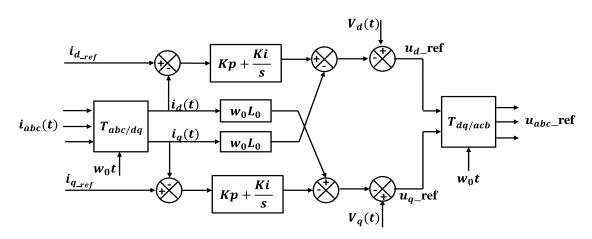

| Figure 2.10 Control structure of phase current controllers                                                                                                                          | 22 |

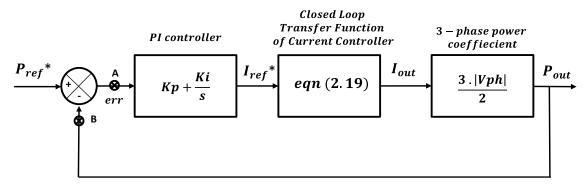

| Figure 2.11 Block diagram of Active Power control loop                                                                                                                              | 23 |

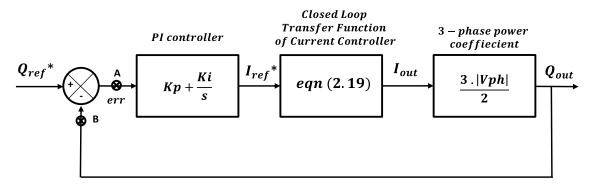

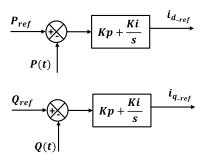

| Figure 2.12 Block diagram of Reactive power control loop                                                                                                                            | 23 |

| Figure 2.13 Control structure of power controllers                                                                                                                                  | 23 |

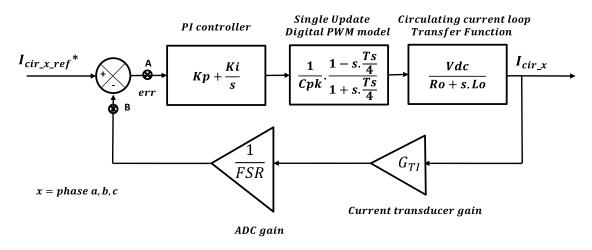

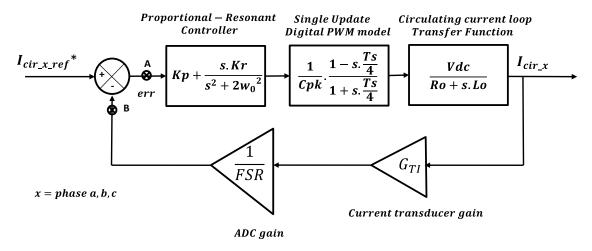

| Figure 2.14 Block diagram of circulating current control loop                                                                                                                       | 24 |

| Figure 2.15 Control structure for circulating current controller                                                                                                                    | 25 |

| Figure 2.16 Simulation system connections between AC and DC bus                                                                                                                     | 26 |

| Figure 2.17 Simulation results (a) Active and Reactive powers (b) Grid voltages (c) Gricurrents (d) DC current (e) Circulating current (f) Upper arm three-phase capacitor voltages |    |

| Figure 2.18 Performance of circulating current controller (enabled at 0.15sec)                                                                                                                                                                                                                                     | . 29 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Figure 2.19 Performance of conventional voltage balancing method                                                                                                                                                                                                                                                   | . 29 |

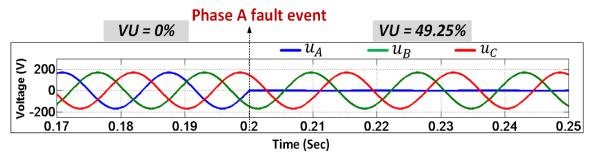

| Figure 3.1 Grid voltage unbalance test-case for simulation                                                                                                                                                                                                                                                         | . 31 |

| Figure 3.2 Various d-q axis components (a) d-axis grid voltage (b) q-axis grid voltage d-axis phase current controller reference generated by active power controller (d) q-axis phase current controller reference generated by reactive power controller                                                         | is   |

| Figure 3.3 Various reference signals (a) Converter voltage modulating signal generated by phase current controllers (b) Circulating current modulating signal generated by circulating current controllers (c) Upper arm complete normalized modulating signal (d) Lower arm complete normalized modulating signal | d)   |

| Figure 3.4 Performance of traditional MMC control scheme under unbalance supply voltage (a) Grid voltages (b) Grid currents (C) Active and Reactive powers (d) DC current (e) Circulating current (f) Upper arm three-phase capacitor voltages                                                                     | . 34 |

| Figure 3.5 Frequency spectrum of phase currents during unbalance condition                                                                                                                                                                                                                                         | . 35 |

| Figure 3.6 Circulating current frequency spectrum during unbalance                                                                                                                                                                                                                                                 | . 35 |

| Figure 4.1 Three phase system with active power                                                                                                                                                                                                                                                                    | . 39 |

| Figure 4.2 Three-Phase system with reactive power                                                                                                                                                                                                                                                                  | . 40 |

| Figure 4.3 Three-Phase system equivalent circuit with both active and reactive powers                                                                                                                                                                                                                              | 40   |

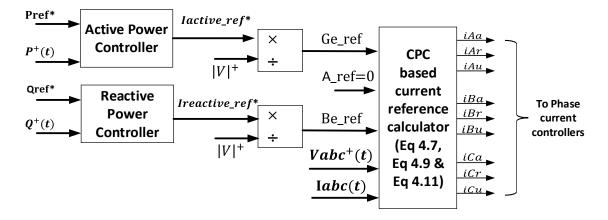

| Figure 4.4 Complete CPC based control structure for MMC                                                                                                                                                                                                                                                            | . 46 |

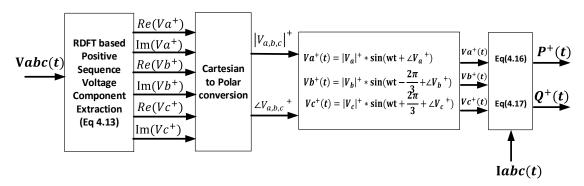

| Figure 4.5 CPC based current control loop block diagram                                                                                                                                                                                                                                                            | . 48 |

| Figure 4.6 CPC based phase current control block diagram                                                                                                                                                                                                                                                           | . 49 |

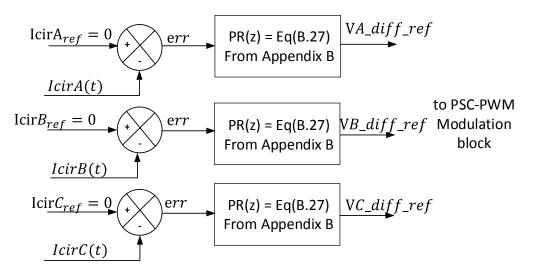

| Figure 4.7 Circulating Current control loop block diagram                                                                                                                                                                                                                                                          | . 50 |

| Figure 4.8 PR circulating current controller block diagram                                                                                                                                                                                                                                                         | . 51 |

| Figure 4.9 Block diagram of Instantaneous power computations                                                                                                                                                                                                                                                       | . 52 |

| Figure 4.10 Block diagram of Power controllers interface with phase current controllers                                                                                                                                                                                                                            | . 53 |

| Figure 4.11 CPC based control performance under Balance supply condition                                                                                                                                                                                                                                           | . 54 |

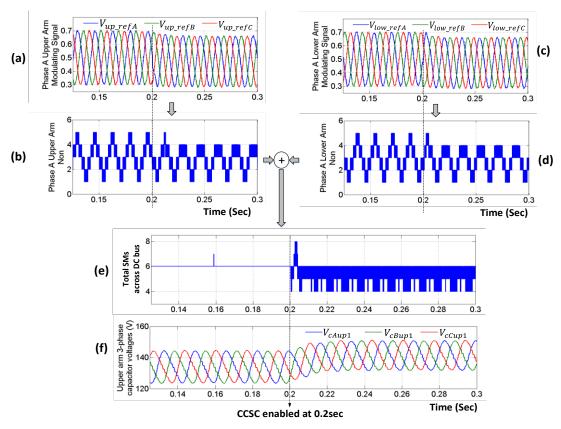

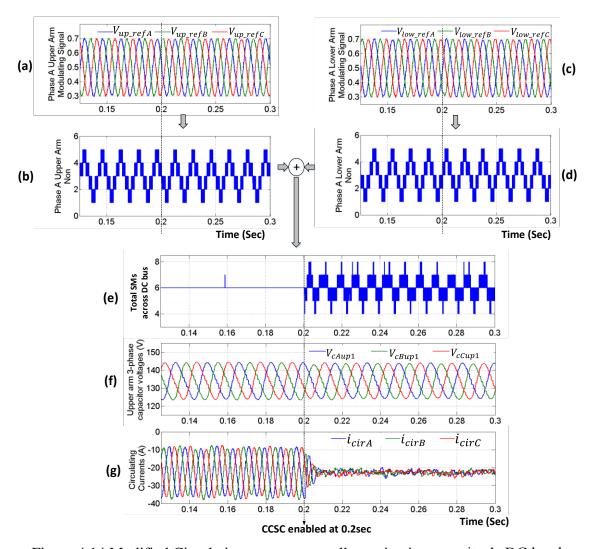

| Figure 4.12 Effect of circulating control on modulating signals, NON and capacitor voltages                                                                                                                                                                                                                        | . 57 |

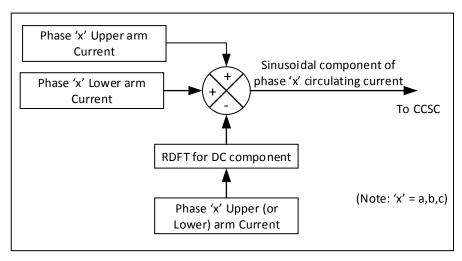

| Figure 4.13 Block diagram of circulating current's 2nd harmonic extraction                                                                  | 58 |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 4.14 Modified Circulating current controller maintains capacitor's DC level                                                          | 59 |

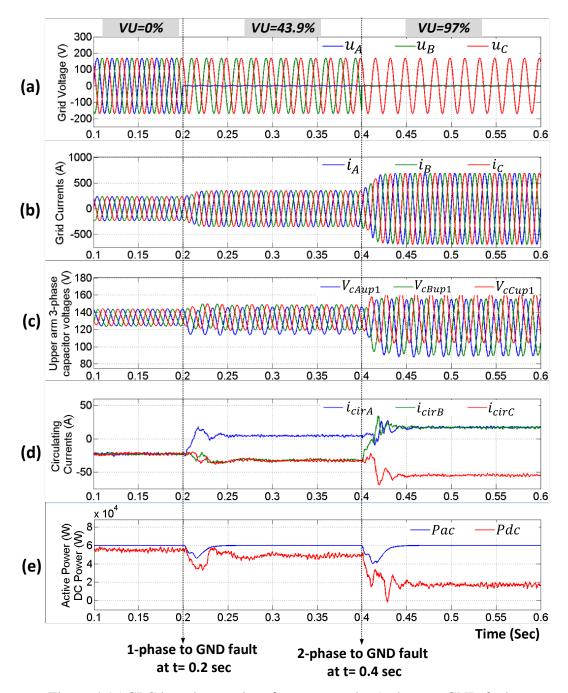

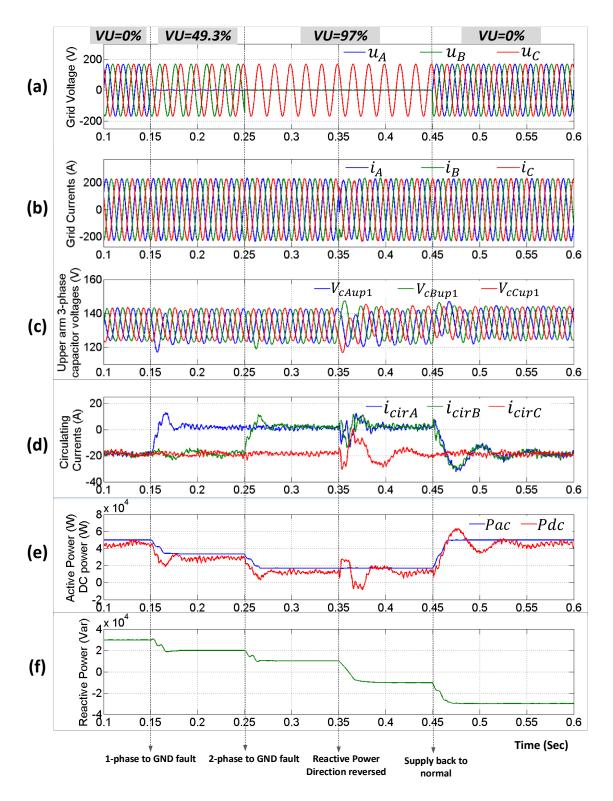

| Figure 4.15 CPC based control performance under 1-phase to GND fault                                                                        | 62 |

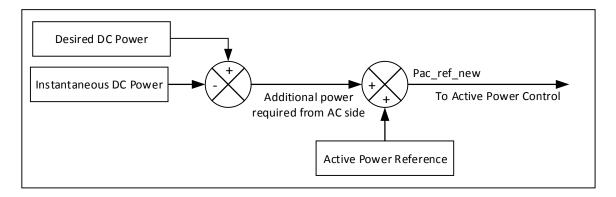

| Figure 4.16 Method for keeping DC side power constant                                                                                       | 64 |

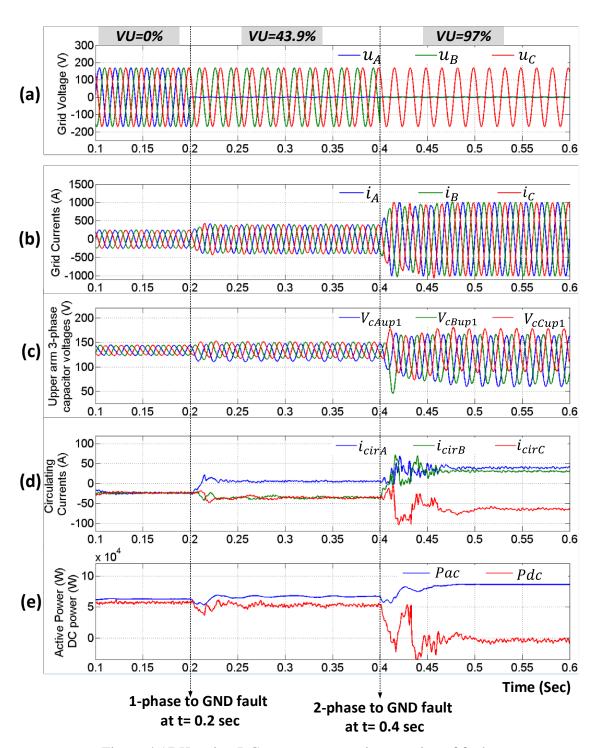

| Figure 4.17 Keeping DC power constant irrespective of fault                                                                                 | 65 |

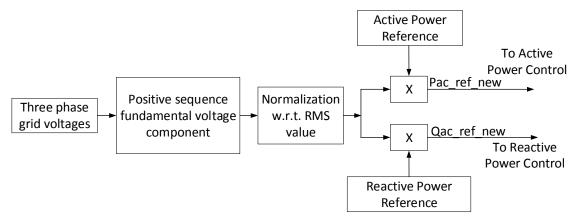

| Figure 4.18 Method to maintain phase current within constraints                                                                             | 67 |

| Figure 4.19 Keeping phase currents constant irrespective of fault                                                                           | 68 |

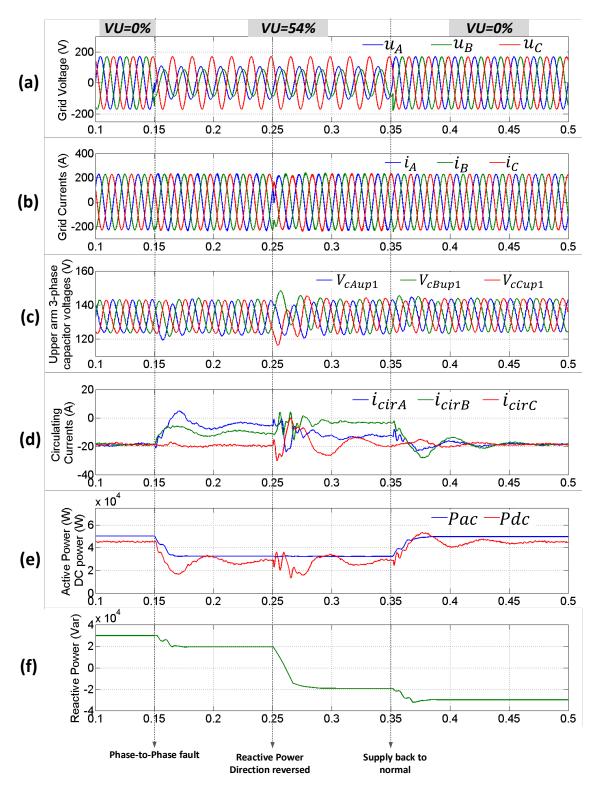

| Figure 4.20 Phase to phase fault creation method                                                                                            | 69 |

| Figure 4.21 Performance under phase-to-phase fault                                                                                          | 70 |

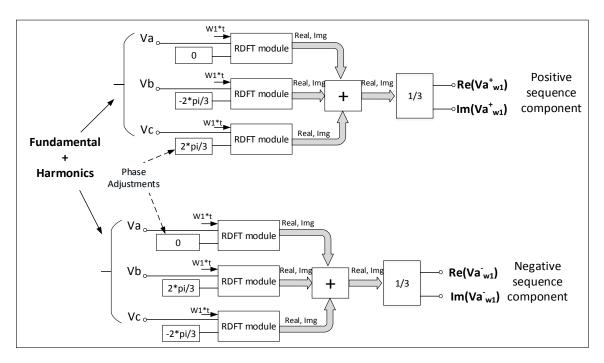

| Figure 4.22 RDFT based fundamental frequency and symmetric component extraction                                                             | 72 |

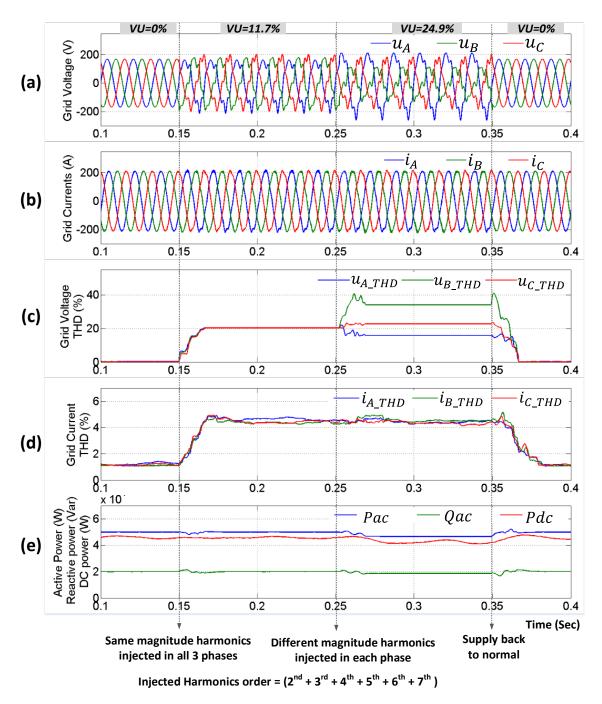

| Figure 4.23 Performance under non-sinusoidal supply conditions                                                                              | 73 |

| Figure 5.1 MMC phase leg with average model of arm capacitance                                                                              | 76 |

| Figure 5.2 Equivalent circuit of circulating current model                                                                                  | 81 |

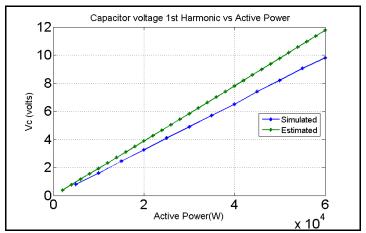

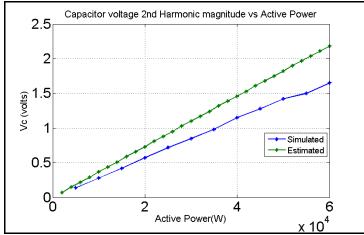

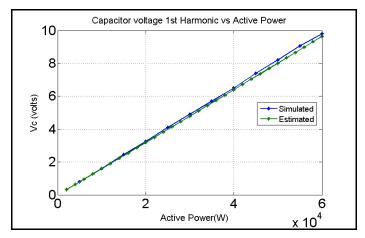

| Figure 5.3 Simulation and Average model comparison for Vcw1_pk vs Active power                                                              | 82 |

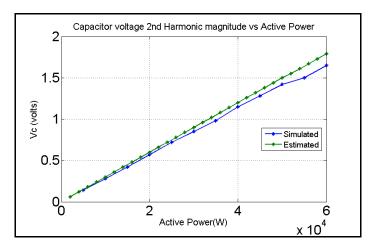

| Figure 5.4 Simulation and Average model comparison for Vcw2_pk vs Active power                                                              | 82 |

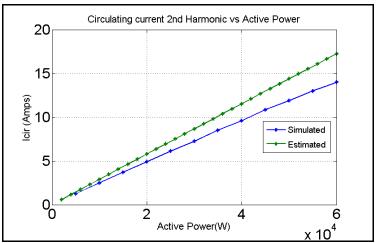

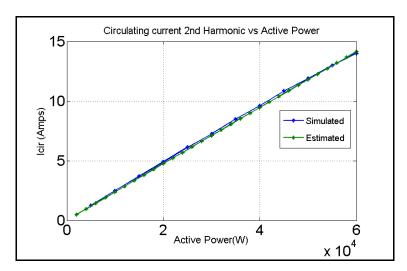

| Figure 5.5 Simulation and Average model comparison for Icir_pk vs Active power                                                              | 83 |

| Figure 5.6 Simulation and Average model comparison for Capacitor voltage peak fundamental ripple vs Active power (with error compensation)  | 84 |

| Figure 5.7 Simulation and Average model comparison for Capacitor voltage peak 2nd harmonic ripple vs Active power (with error compensation) | 84 |

| Figure 5.8 Simulation and Average model comparison for circulating current peak vs Active power (with error compensation)                   | 85 |

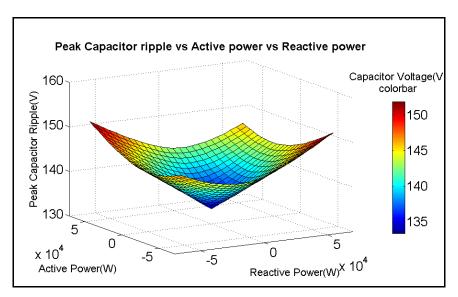

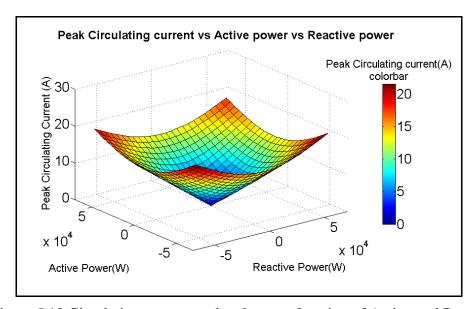

| Figure 5.9 Capacitor peak voltage as a function of Active and Reactive Power                                                                | 86 |

| Figure 5.10 Circulating current peak value as a function of Active and Reactive Power                                                       | 86 |

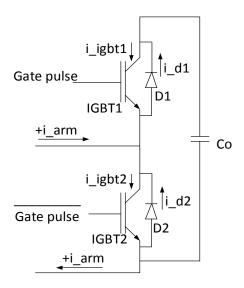

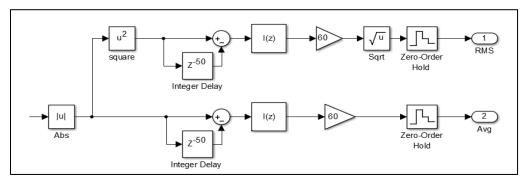

| Figure 5.11 Various paths Arm current can take through a sub-module                                                                         | 90 |

| Figure 5.12 RMS and average current computation block diagram                                                                               | 90 |

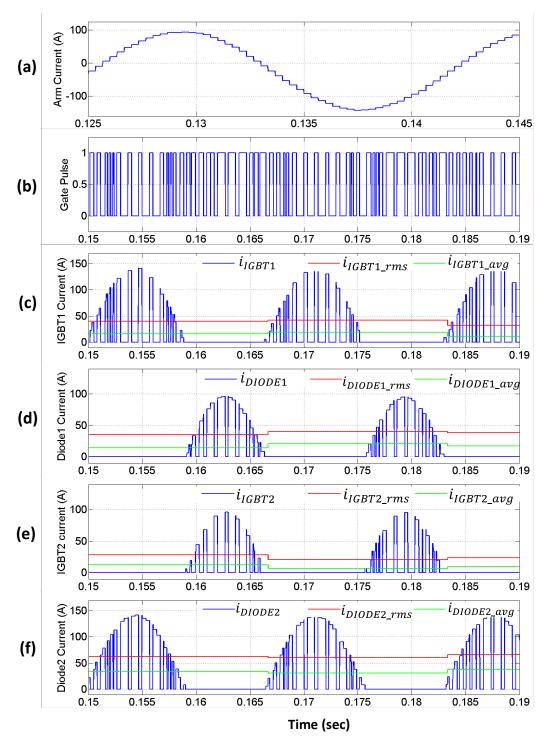

| Figure 5.13 Extraction of individual semiconductor currents using arm current and submodule gate pulse. (a) Arm current (b) sub-module gate pulse (c) IGBT1 current (d) Diode1 current (e) IGBT2 current (f) Diode2 current |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

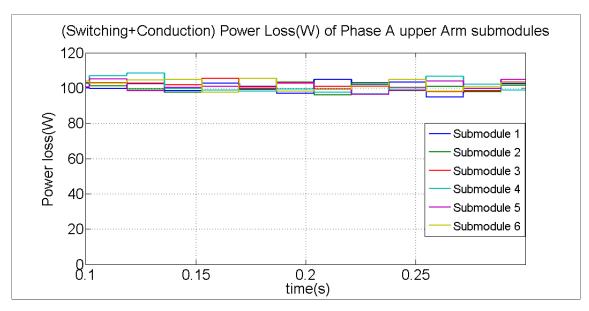

| Figure 5.14 Power loss comparison of all sub-modules in an Arm                                                                                                                                                              |

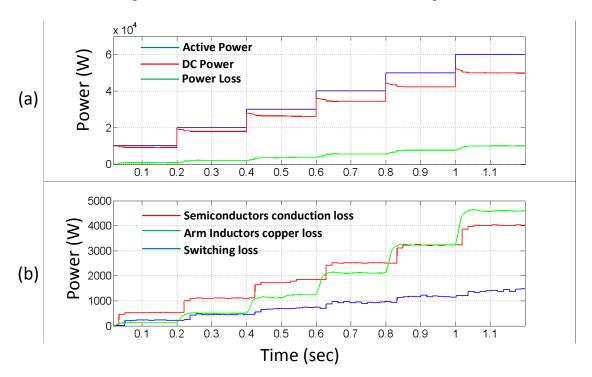

| Figure 5.15 Powers under balance conditions (a) Active power, DC power and power loss (b) Total switching, conduction and copper losses                                                                                     |

| Figure 5.16 Power transfer using reference reduction method (from chapter 4)95                                                                                                                                              |

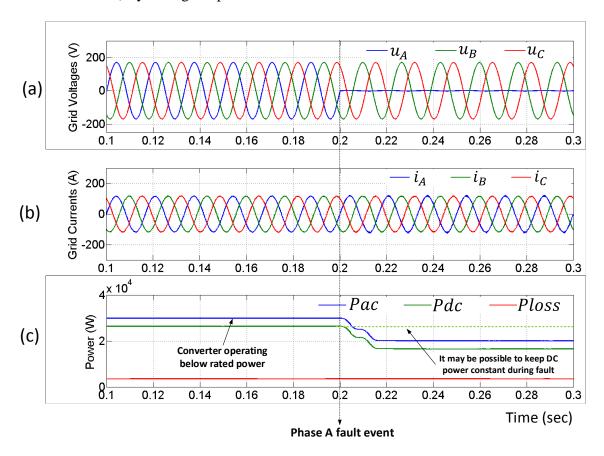

| Figure 5.17 Converter operating below rated power during fault                                                                                                                                                              |

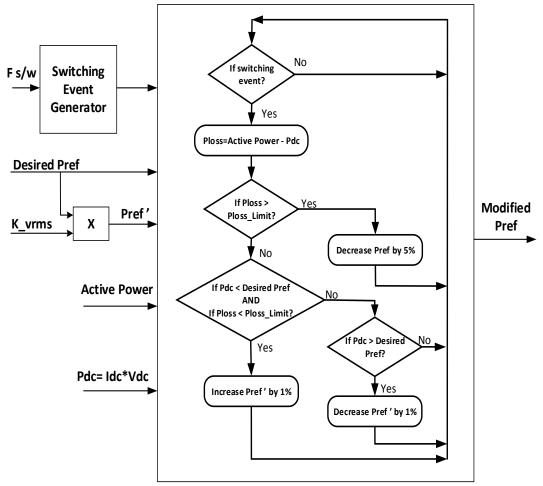

| Figure 5.18 Power reference modification algorithm (using DC current RMS value) 99                                                                                                                                          |

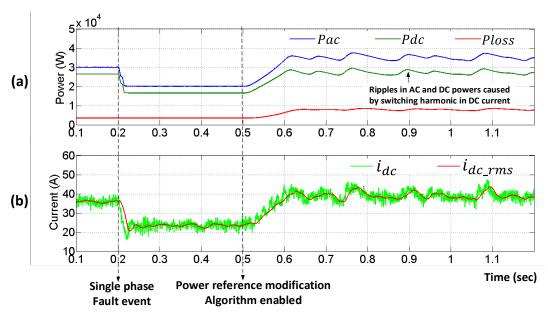

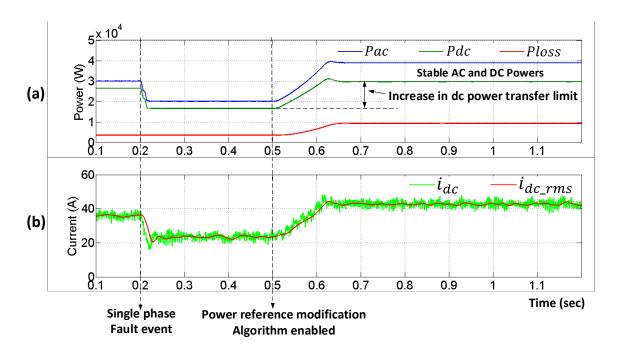

| Figure 5.19 Performance of power reference modification algorithm (using DC current)                                                                                                                                        |

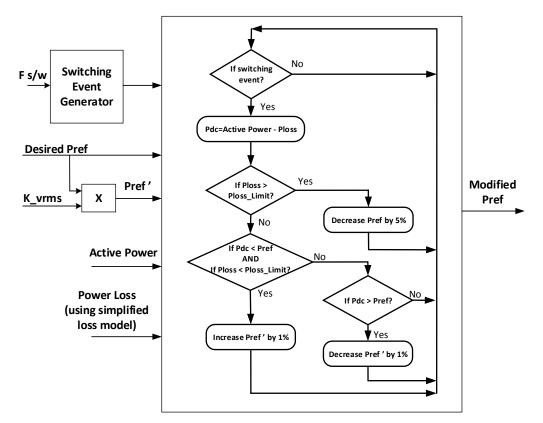

| Figure 5.20 Power reference modification algorithm (using simplified Loss model) 101                                                                                                                                        |

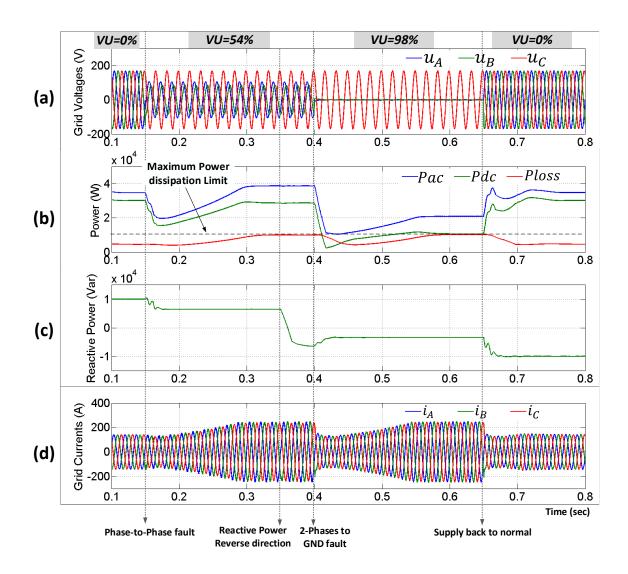

| Figure 5.21 Performance of power reference modification algorithm (using Loss model)                                                                                                                                        |

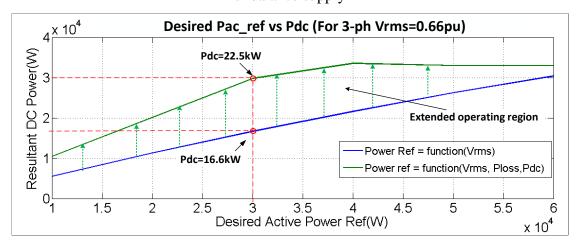

| Figure 5.22 Performance of proposed method to extend the dc power transfer limit during unbalance supply                                                                                                                    |

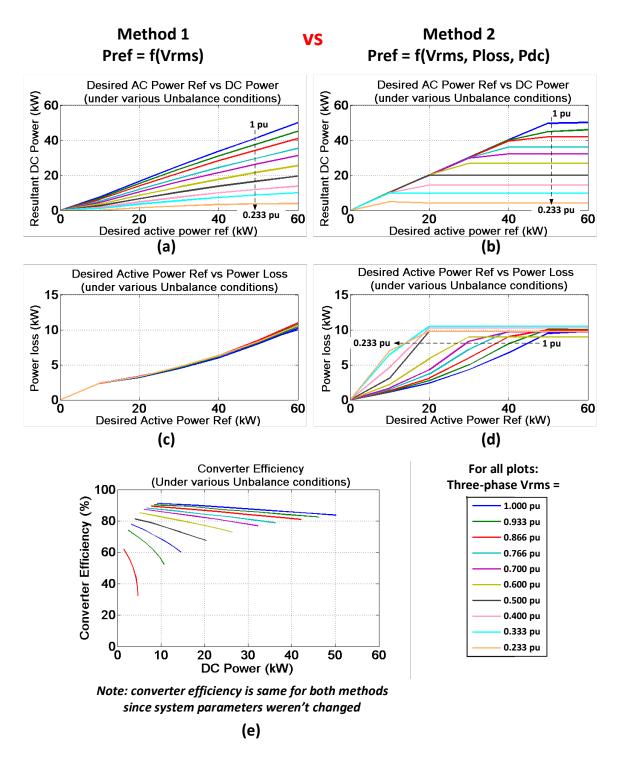

| Figure 5.23 Comparison of two power reference modification methods during unbalance                                                                                                                                         |

| Figure 5.24 Comparison of performance of two active power reference modification methods for various unbalance test cases                                                                                                   |

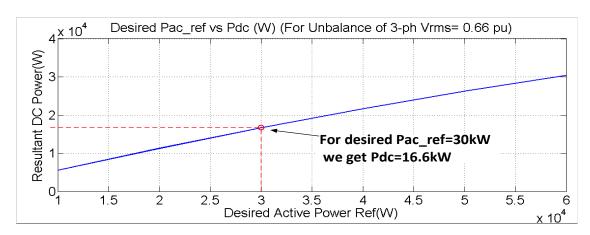

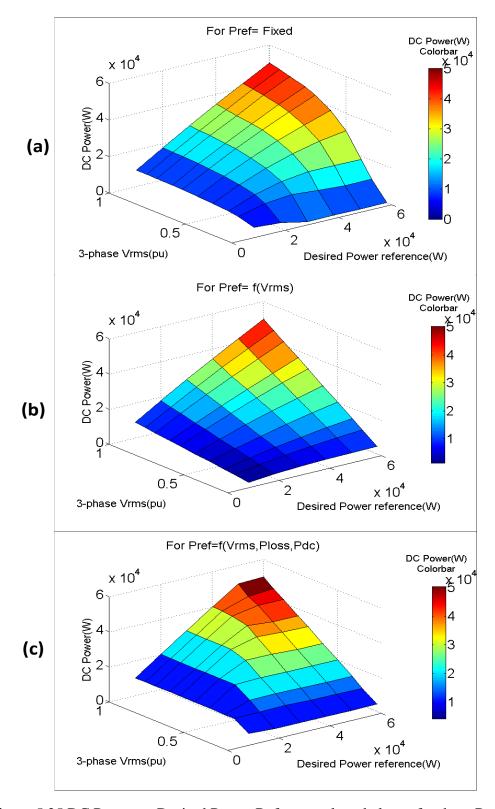

| Figure 5.25 DC Power vs Desired Power Ref vs supply unbalance for three Ref calculation methods                                                                                                                             |

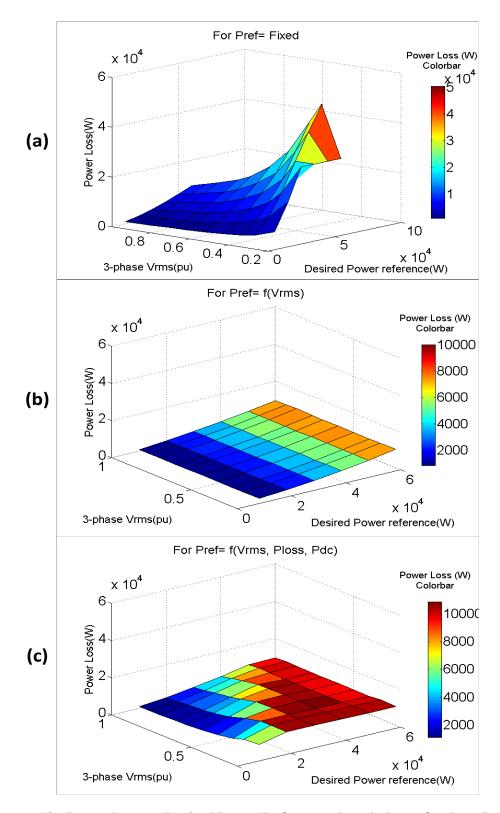

| Figure 5.26 Power Loss vs Desired Power Ref vs supply unbalance for three Ref calculation methods                                                                                                                           |

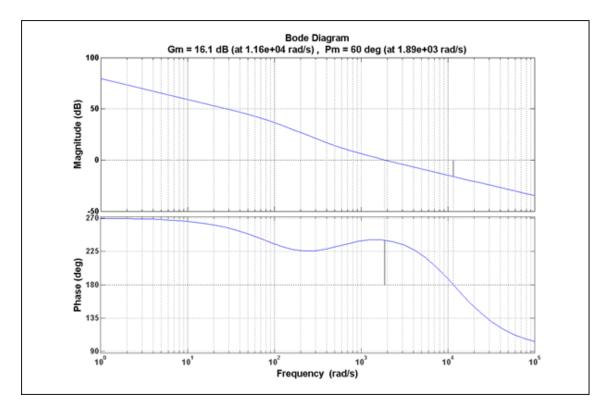

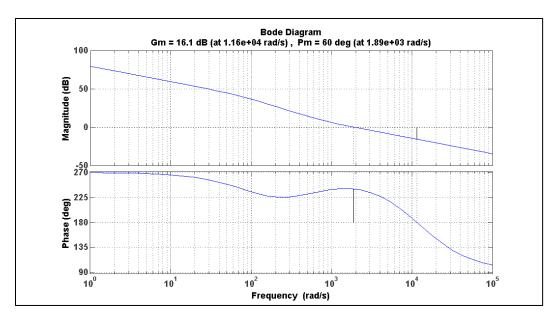

| Figure A.1 Bode plot of traditional phase current controller open loop TF 121                                                                                                                                               |

| Figure A.2 Bode plot of power controller open loop TF                                                                                                                                                                       |

| Figure A.3 Bode plot of traditional circulating current controller open loop TF 126                                                                                                                                         |

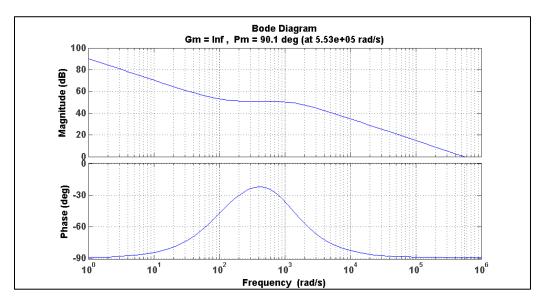

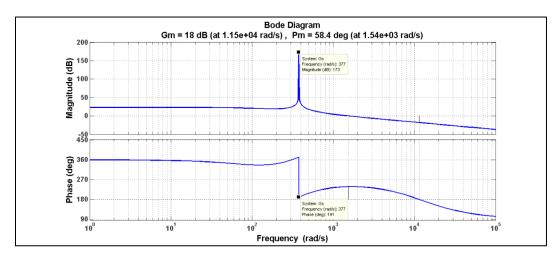

| Figure B.1 Bode plot of CPC phase current control loop                                                                                                                                                                      |

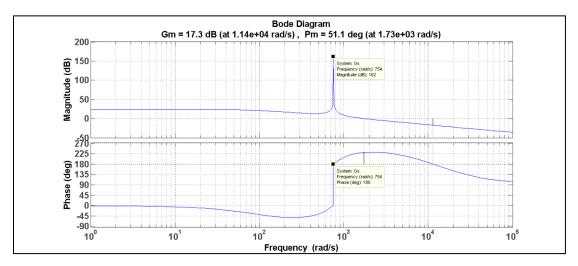

| Figure B.2 Bode plot of PR circulating current controller loop | 133 |

|----------------------------------------------------------------|-----|

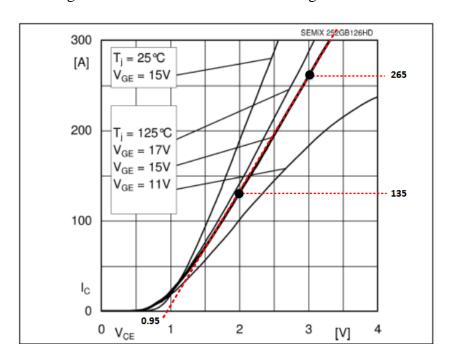

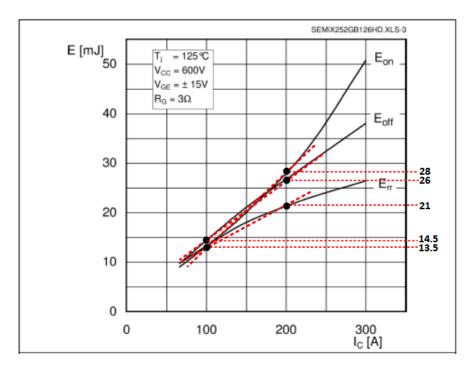

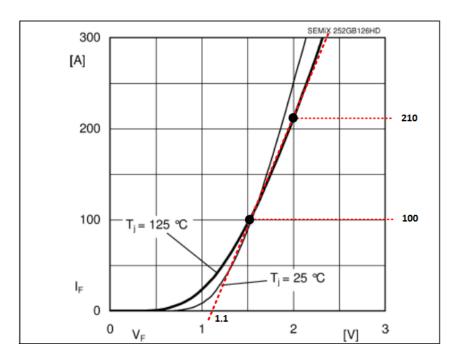

| Figure C.1 IGBT Forward Characteristics                        | 135 |

| Figure C.2 Turn ON/OFF Energy Loss                             | 136 |

| Figure C.3 Diode Forward Characteristics                       | 137 |

## LIST OF ABBREVIATIONS

| AC              |                                       |

|-----------------|---------------------------------------|

| ADC             | Analog to Digital Converter           |

| CPC             | Current's Physical Components         |

| DSP             | Digital Signal Processor              |

| DC              | Direct Current                        |

| emf             |                                       |

| IGBT            | Insulated Gate Bipolar Transistor     |

| MMC             | Modular Multi-level Converter         |

| N <sub>ON</sub> | Number of sub-modules to be turned on |

| PI              | Proportional Integral                 |

| PR              | Proportional Resonant                 |

| PSC-PWM         | Phase-shifted Carrier-based PWM       |

| PWM             | Pulse Width Modulation                |

| RDFT            | Recursive Discrete Fourier Transform  |

| RMS             | Root Mean Square                      |

| VB              | Voltage Balancing                     |

| VSC             | Voltage Source Converter              |

| THD             | Total Harmonic Distortion             |

#### CHAPTER 1

#### INTRODUCTION

The Modular Multilevel Converter (MMC) concept was introduced over a decade ago by Lesnicar and Marquardt[1]. It is a promising technology that has caught the attention of many research groups in industry and academia, because of several technical and economic benefits such as modularity, scalability, low voltage distortion, failsafe operations etc.

Modular Multilevel Converters consist of series connections of sub-modules (also called static cells). This modular structure permits design of high-voltage converters handling hundreds of kilovolts without direct series connection of the power semiconductor devices as in two or three level converters. Additionally, the large number of voltage levels reduces the filtering requirement on both DC and AC side of a converter even at very low switching frequency.

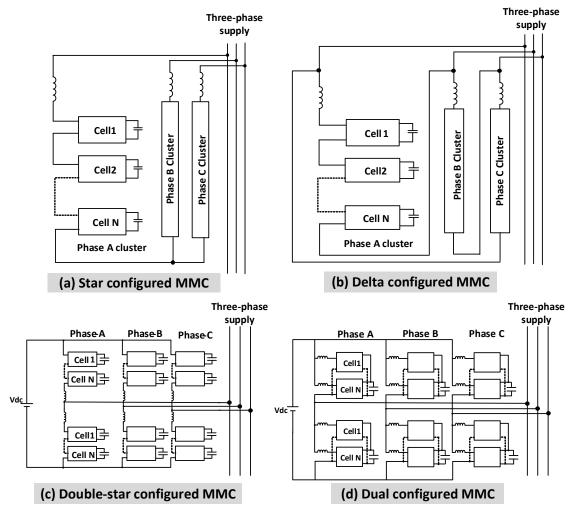

Figure 1.1 shows the classification of three-phase MMCs based on sub-module (SM) structure (half bridge or full bridge) [2]. In general MMCs can be classified into:

- 1) Star configured MMC

- 2) Delta configured MMC

- 3) Double star-configuration MMC

- a) Half-bridge MMC

- b) Full-bridge MMC

#### 4) The dual MMC

Figure 1.1 Circuit configurations of MMC (a) Star configured MMC (b) Delta configured MMC(c) Double star Configured MMC (d) The Dual MMC

Figure 1.1 (a) & (b) shows the star/delta-configured MMC topology. These configurations do not have common dc-link terminals and therefore these star-delta configurations mostly find applications in STATCOMs and energy storage systems [3]. Figure 1.1 (c) shows the double-star-configured MMC topology which possesses a common dc-link. Due to its structure this configuration can be used for interfacing AC

and DC system for achieving bidirectional power transfer between those systems. Therefore the double-star topology is highly suitable for utility related converter applications. Another MMC topology is shown in Figure 1.1 (d) which is called Dual MMC. In this case, each dc side of positive and negative chopper-cells possesses a common dc capacitor, whereas its ac side is connected in parallel via buffer inductors. It is mainly used for low-voltage large-power conversion applications [3].

The double-star MMC configuration, which is the most suitable for utility applications, needs to handle various grid supply related issues such as phase-to-ground faults, phase-to-phase faults, non-sinusoidal supply caused by harmonic generating loads, etc. A control strategy must be provided that protects MMC systems and delivers the best possible performance during such non-ideal AC grid conditions. In order to achieve that, a novel method for control of double-star topology MMCs under non-ideal AC side conditions is presented in this dissertation. The dissertation outlines a traditional control method in chapter 2 and elucidates the limits of such control systems under non-ideal supply conditions in chapter 3. A new control strategy is presented in chapter 4 that achieves the desired performance criteria during unbalance supply conditions and then chapter 5 develops a novel method for estimating and extending the operating region of a MMC during asymmetrical supply conditions. The traditional control method described in chapter 2 serves as the baseline of comparison for validating the performance of the proposed control method.

#### CHAPTER 2

# MODELING AND TRADITIONAL CONTROL OF MODULAR MULTILEVEL CONVERTERS

This chapter describes dynamic modeling of the double star MMC configuration and selection of its passive elements. It also provides a background literature survey on MMC control methods and then develops a commonly used control approach along with simulation results.

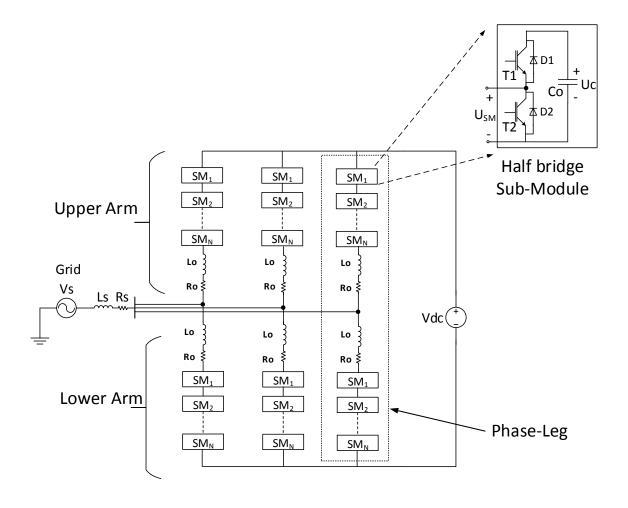

#### 2.1 OVERVIEW OF DOUBLE-STAR CONFIGURATION MMC

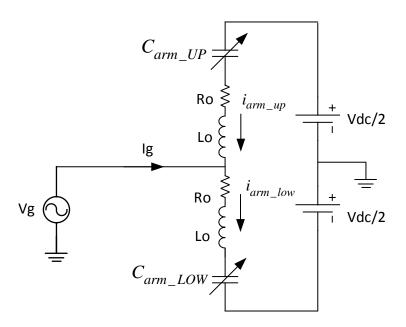

Figure 2.1 shows a three-phase MMC double-star structure using half-bridge IGBT sub-modules. A six-level half-bridge MMC will be investigated in this dissertation for achieving various performance objectives. Although more many more levels are typically used, six levels are sufficient for investigations without loss of generality and match a hardware laboratory prototype that is available for future validation of this work. The following section focuses on developing a mathematical model of a double-star MMC and design of the commonly used closed loop control system for MMCs used in utility applications.

Figure 2.1 Half-bridge three-phase Modular Multilevel Converter

#### 2.2 MMC MODELING

Various modeling methods have been explored in the literature for targeted applications of the MMC. For modeling purpose many authors assume that voltage across each sub-module capacitor remains ideal. This assumption helps to derive simple dynamic equations of the MMC. Without this assumption modeling would be much more complicated because of the different voltages across each sub-module caused by bidirectional current flowing through them.

Reference [4] derives a continuous domain model of a MMC by representing the system with ordinary differential equations which are then solved by numerical integration methods. The continuous model accurately describes lower order harmonics. Frequency domain approaches have been attempted by [5] & [6]. Reference [5] decouples the MMC circuit into separate AC and DC parts using linear transformation and then the sub-module variables are computed using iterated convolution. The method is used with an optimization algorithm to extend the operating region of MMC for given grid and converter parameters. The analysis and prediction of harmonic content in arm currents and sub-module capacitors was investigated in the frequency domain by the application of Fourier series in [6].

Other modeling approaches have been proposed in references [7], [8], [9], [10], [11], [12]. In general, there are three main parameters to be considered for MMC modeling: arm currents, output currents and sub-module capacitor voltages. Reference [11] has proposed a modeling method based on energy stored in the upper and lower arms of each phase. The mathematical equations for total energy in an arm and difference between upper and lower arm energy are derived and used for control purpose. Whereas, a switching function based modeling technique is implemented by [12].

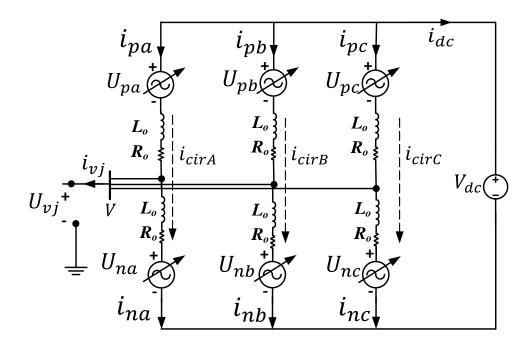

In this dissertation the MMC dynamics are derived based on [10] & [11] since it covers various aspects of MMC design and simulation. The model mainly focuses on arm current, sub-module capacitor voltage and circulating current dynamics. These dynamics are formulated by using first order differential equations of arm currents and inner difference voltages of each phase. In order to develop the model consider Figure 2.2 which shows the detailed circuit of the three-phase MMC where *Lo* and *Ro* are the arm

inductance and equivalent resistance respectively. Vdc and Idc are total DC side voltage and current respectively. The MMC output voltage is denoted by  $U_{vj}$  and phase currents are denoted by  $i_{vj}$  where j=a,b,c. The arm voltage generated by cascade connection of Sub-modules is expressed by  $U_{pj}$  and  $U_{nj}$  where the sub-script p & n refers to the upper and lower arm respectively.

Figure 2.2 MMC with equivalent circuit of sub-modules

From Figure 2.2 the upper and lower arm currents  $i_{pj} \& i_{nj}$  can be expressed as

$$i_{pj} = i_{diffj} + \frac{i_{vj}}{2} \tag{2.1}$$

$$i_{nj} = i_{diffj} - \frac{i_{vj}}{2} \tag{2.2}$$

Where  $i_{diffj}$  represents the difference current or circulating current of phase j which flows through both upper and lower arms and it is expressed as average of both upper and lower arm currents,

$$i_{diffj} = \frac{i_{pj} + i_{nj}}{2} \tag{2.3}$$

According to [10] & [11] the MMC can be characterized by equations (2.4)-(2.9).

Output voltage is given by,

$$Uvj = e_j - \frac{Ro}{2} \cdot i_{vj} - \frac{Lo}{2} \cdot \frac{di_{vj}}{dt}$$

(2.4)

DC loop equation of each MMC arm is given by,

$$Lo.\frac{di_{diffj}}{dt} + Ro.i_{diffj} = \frac{U_{dc}}{2} - \frac{u_{pj} + u_{nj}}{2}$$

$$(2.5)$$

Inner emf generated in phase 'j' is given by,

$$e_j = \frac{u_{nj} - u_{pj}}{2} \tag{2.6}$$

According to equation (2.4) the output phase current  $i_{vj}$  can be directly controlled by regulating control variable  $e_j$ . This allows to use a current vector control scheme based on d-q coordinates which ideally guarantees zero steady-state error.

Inner difference voltage of phase j is given by,

$$u_{diffj} = Lo.\frac{di_{diffj}}{dt} + Ro.i_{diffj}$$

$$u_{diffj} = \frac{U_{dc}}{2} - \frac{u_{pj} + u_{nj}}{2}$$

(2.7)

Equation (2.7) shows that the difference current  $i_{diffj}$  can be controlled by regulating difference (unbalance) voltage  $u_{diffj}$ . Therefore from equations (2.6) and (2.7) the reference voltages for upper and lower arms are derived as give below:

$$u_{pj\_ref} = \frac{U_{dc}}{2} - e_j - u_{diffj} \tag{2.8}$$

$$u_{nj\_ref} = \frac{U_{dc}}{2} + e_j - u_{diffj} \tag{2.9}$$

The circulating current is generated by the voltage imbalances among each phase leg and it is mainly composed of negative sequence  $2^{\rm nd}$  harmonic component [10]. In equations (2.8) and (2.9) it the same difference voltage (which is mainly responsible for circulating current) is subtracted from both the upper and lower arm voltage references. Thus the resulting  $e_j$  will not change and the AC side dynamics are unaffected by the circulating current. However, the circulating current increases the RMS value of arm currents and therefore causes higher converter losses (through arm inductors, capacitors and semiconductors).

Ideally, in steady state, the circulating current should be zero, but because of leg voltage imbalances the circulating current would have a 2<sup>nd</sup> order harmonic current superimposed on the existing arm current. In the time domain, the circulating currents of three phases could be expressed as combination of DC and AC parts as given below,

$$i_{diffa} = \frac{I_{dc}}{3} + I_{2f} \sin(2w_o t + \varphi_o)$$

(2.10)

$$i_{diffb} = \frac{I_{dc}}{3} + I_{2f} \sin(2w_o t + \frac{2\pi}{3} + \varphi_o)$$

(2.11)

$$i_{diffc} = \frac{I_{dc}}{3} + I_{2f} \sin(2w_o t - \frac{2\pi}{3} + \varphi_o)$$

(2.12)

Where,  $I_{dc}$  is total DC current as shown in Figure 2.2.  $I_{2f}$  is the peak value of  $2^{nd}$  harmonic circulating current,  $w_0$  is the fundamental frequency and  $\varphi_0$  is the initial phase angle.

According to [13] and [14] three-phase currents can be transformed into two dc components by applying the Park transformation to the three phase current equations. This transformation is also known as a-b-c to d-q transformation. The transformation is done on fundamental line frequency rotational reference frame for phase currents whereas on double line frequency negative sequence rotational reference frame for circulating currents. The Park transformation matrix is given by,

$$T_{acb/dq} = \frac{2}{3} \begin{bmatrix} \cos\theta & \cos(\theta - \frac{2\pi}{3}) & \cos(\theta + \frac{2\pi}{3}) \\ -\sin\theta & -\sin(\theta - \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) \end{bmatrix} \dots (\theta = 2w_{ot}t)$$

(2.13)

and corresponding inverse Park transformation is given by,

$$T_{dq/acb} = \frac{2}{3} \begin{bmatrix} \cos(\theta) & -\sin(\theta) \\ \cos(\theta - \frac{2\pi}{3}) & -\sin(\theta - \frac{2\pi}{3}) \\ \cos(\theta + \frac{2\pi}{3}) & -\sin(\theta + \frac{2\pi}{3}) \end{bmatrix} \dots (\theta = 2w_{ot}t)$$

$$(2.14)$$

Equation (2.7) can be written in vector form as,

$$\begin{bmatrix} u_{diffa} \\ u_{diffc} \\ u_{diffb} \end{bmatrix} = Lo.\frac{d}{dt} \begin{bmatrix} i_{diffa} \\ i_{diffc} \\ i_{diffb} \end{bmatrix} + Ro \begin{bmatrix} i_{diffa} \\ i_{diffc} \\ i_{diffb} \end{bmatrix}$$

(2.15)

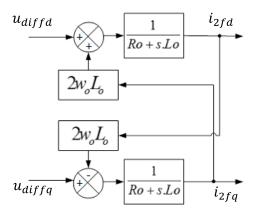

Substituting (2.10), (2.11) and (2.12) in (2.15) and applying the park transformation matrix of (2.13),

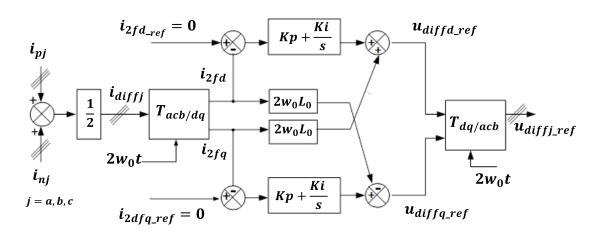

$$\begin{bmatrix} u_{diffd} \\ u_{diffq} \end{bmatrix} = Lo.\frac{d}{dt} \begin{bmatrix} i_{2fd} \\ i_{2fq} \end{bmatrix} + \begin{bmatrix} 0 & -2w_oL_o \\ 2w_oL_o & 0 \end{bmatrix} \cdot \begin{bmatrix} i_{2fd} \\ i_{2fq} \end{bmatrix} + Ro \begin{bmatrix} i_{2fd} \\ i_{2fq} \end{bmatrix}$$

(2.16)

Here,  $u_{diffd}$  and  $u_{diffq}$  are d-q components of difference voltage and  $i_{2fd}$  and  $i_{2fq}$  are d-q components of circulating current. The  $2w_0L_0$  and  $-2w_0L_0$  terms show the cross-coupling between d and q axis components. By using (2.16) the transfer function block diagram of circulating current [10] can be represented as shown in Figure 2.3.

Figure 2.3 Circulating Current Transfer Function

#### 2.3 SELECTION OF ARM INDUCTACE AND SUBMODULE CAPACITANCE

Two main aspects of MMC design are dimensioning of sub-module capacitors and arm inductors. In [15] a design principle is described for design of arm inductor

based on two distinctive functions: suppressing circulating current and limiting fault current rise rate. Reference [16] discusses dimensioning of SM capacitor for MMC by considering voltage limits of SM with voltage. Using [15] and [16] the selection of arm inductor and sub-module capacitor is done as shown below.

The formula for selection of sub-module capacitor is given by equation (2.17).

$$C = \frac{P}{3 k N w_o e V_c^2} \left[ 1 - \left( \frac{k \cos(\emptyset)}{2} \right)^2 \right]^{\frac{3}{2}}$$

(2.17)

The formula for selection of arm inductance is given by equation (2.18).

$$L = \frac{1}{8 w_o^2 C V_c} \left[ \frac{P}{3 I_{2f}} + V_{dc} \right]$$

(2.18)

Given parameters are,

$$P = 60e3VA; N = 6; w_o = 2*pi*60 \frac{rad}{s}; V_c = 133.33V; Vdc = 800V;$$

$$I_{2f} = 15\text{A}; \ k = 0.3; \cos(\phi) = 1; e = 10\%$$

For the above given parameters the sub-module capacitance is found to be 16.4mF. A choice was made to use 15mF based on market available capacitors size, cost, ESR and availability. Using 15mF as a sub-module capacitor now the arm inductance can be designed based on equation (2.18). The resulting value found for arm inductor is 0.938mH. A choice was made to use 1mH based on cost, size, weight and availability.

#### 2.4 MMC CONTROL STRUCTURE

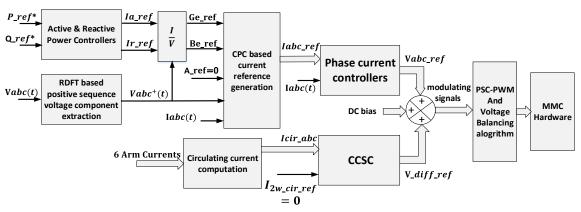

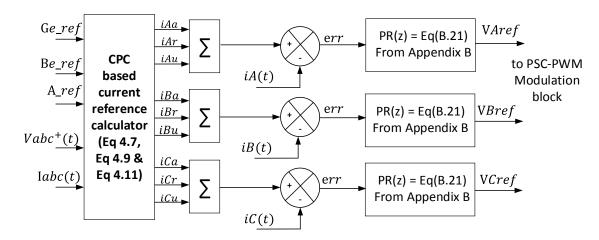

Figure 2-4 shows the block diagram of a typical control structure of a MMC. The control structure consists of three main components: multilevel modulation, voltage balancing algorithm and closed loop controllers for achieving desired power conversion objectives. The closed loop controller has three types of controllers namely, inner phase current controller, outer power controller and circulating current controller.

This section focuses on MMC modulation schemes, voltage balancing techniques and closed loop control approaches that have been implemented so far in the known literature. Based on the background research and literature survey a commonly used modulation, voltage balancing and controller design approach is selected to design a simulation model to understand the basics of MMC and issues related to control technique.

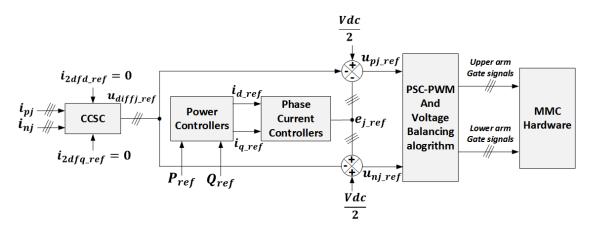

Figure 2.4 Complete control structure of a MMC

#### 2.4.1 MULTI-LEVEL MODULATION TECHNIQUES

Various modulation techniques have been investigated over the last decade.

Considering the MMC structure, the switching loss is directly proportional to number of

MMC levels; therefore switching frequency reduction technique has been the core of many modulation methods. Authors of [17], [18], [19] have implemented Sub-module Unified Pulse Width Modulation (SUPWM). Reference [17] implements SUPWM by using 180 deg. phase shifted carrier signal for upper and lower arms. This method achieves sub-module voltage balancing for single phase MMC without using a closed loop control for capacitor voltage balancing. However, the performance of this technique remains unknown for its extension to three-phase MMCs.

Another modulation scheme known as Carrier Shifted Pulse Width Modulation (CS-PWM) is implemented by references [20], [21], [22], [23], [24], [25]. The carrier shifted method is divided in two parts: Phase shifted and Level Shifted. In Carrier Phase Shifted PWM (CPSPWM) method 'N' carrier signals are used to create N+1 level inner emf. The phase shift between two consecutive carrier signals is equal to 360/N. Whereas in Level Shifted PWM (LSPWM) each carrier (out of N) has particular DC offset and addition of all carrier offsets is equal to peak amplitude of modulating signal. These two methods could also be combined to implement different variations of carrier shifted PWM such as Phase Disposition(PD), Phase Opposition Disposition(POD), Alternative phase opposition disposition (APOD), Saw-tooth etc. These methods use Sub-module capacitor voltages for close loop control of voltage balancing. Reference [23] implements another variation of carrier shifted PWM in which the modulating waveform is shifted and scaled to bring inside one carrier signal. With this technique the harmonics in the phase voltage are shifted to twice the switching frequency. Reference [1] has implemented a traditional space vector PWM (SVPWM) modulation technique. The

SVPWM method finds limited practical applications because the complexity of algorithm is proportional to the number of levels in MMC.

Apart from conventional modulation techniques some other ideas like fundamental switching frequency with predefined pulse pattern generation [26], stochastic optimal fundamental switching frequency [27] were also proposed.

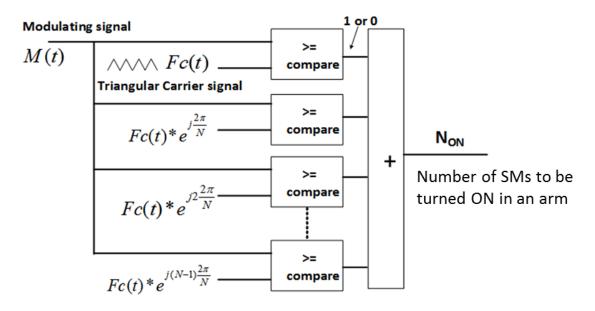

This dissertation uses Phase Shifted Carrier PWM method for modulation purposes. A typical block diagram of PSC-PWM modulation scheme is shown in Figure 2.5.

Figure 2.5 PSC-PWM modulation scheme block diagram

The structure is similar to a traditional sine-triangle modulation where a low frequency modulating signal (usually sinusoidal) is continuously compared with a high frequency triangular shaped signal (also called as a carrier signal). Due to nature of multiple levels in the converter more sine-triangle comparison blocks are required. The total number of compare blocks is equal to the number of sub-module in an arm of MMC. The

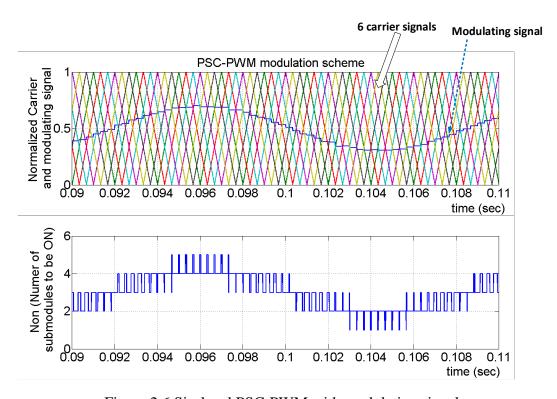

modulating signal is connected to all compare blocks as it is but the carrier signals are connected using different phase-shifts. For 'N' level MMC the phase shift between any two carriers is given by '360/N'. The result of the compare block is either 1 or 0. All the results are added together to produce a signal called as "NoN" which means 'Number of sub-modules to be turned ON in that particular arm. Figure 2.6 shows an example of a six-level PSC-PWM with modulating signal and the resultant 'NoN' signal.

Figure 2.6 Six-level PSC-PWM with modulating signal

#### 2.4.2 Sub-Module voltage balancing

Modular Multilevel Converter voltage imbalance between sub-module capacitors is a significant concern with MMCs. Based on the direction of arm currents the sub-module capacitors would charge or discharge causing the voltage across them to fluctuate about their nominal value. These fluctuations or ripples are proportional to the magnitude

of arm currents. The ripples are also affected by the modulation scheme, semiconductor switching frequency and system sampling frequency used. Many research papers have addressed voltage balancing issues in MMCs [28], [29], [30], [31], [32], [33] and [34].

There are in general two types of sub-module voltage balancing approaches in the literature: open loop and closed loop. In the open loop approach some voltage balancing compensation is added to the modulation scheme. This method does not use any feedback from sub-module capacitors. Whereas in the closed loop approach the sub-module capacitor voltages are measured and used as a feedback to make necessary adjustments in switching of sub-module semiconductors.

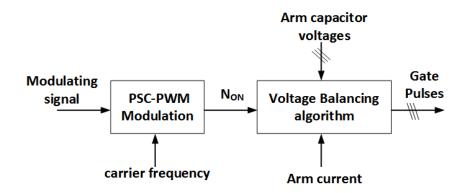

A new voltage balancing algorithm called as Reduced Switching Frequency (RSF) Voltage balancing was proposed by [10] for a 20-level MMC. In this technique the output of PSC-PWM modulation blocks (also known as N<sub>ON</sub>, where N<sub>ON</sub> means Number of Sub-modules to be turned on) is passed to the RSF-VB algorithm. The input parameters for RSF voltage balancing algorithm are upper and lower arm SM capacitor voltages, upper arm current, lower arm currents, upper arm 'N<sub>ON</sub>' and lower arm 'N<sub>ON</sub>'. Based on the direction of individual arm current the measured sub-module voltages are sorted in ascending or descending order. Then depending on the previous and current value of their 'N<sub>ON</sub>' a decision is made whether to keep a sub-module as it is or to turn it ON or to turn it OFF. This technique allows reduction of the average switching frequency of a sub-module below the carrier frequency while keeping the sub-module capacitor voltages well balanced. But this type of reduced switching balancing is only effective if the MMC has a large number of sub-modules. For lower number of sub-modules,

reducing switching frequency further causes degradation of the performance of the voltage balancing algorithm.

In this dissertation a six-level MMC is investigated, therefore, to obtain good voltage balancing the conventional voltage balancing algorithm is used. The block diagram of modulation and voltage balancing scheme is shown in Figure 2.7 and the flow chart for the conventional voltage balancing algorithm is shown in Figure 2.8.

Figure 2.7 Block diagram of Modulation and Voltage balancing scheme

Figure 2.8 Conventional Voltage Balancing Algorithm

#### 2.4.3 CLOSED LOOP CONTROLLERS DESIGN

Various MMC control methods have been investigated by references [35], [36], [37], [38], [39], [40], [41], [42], [43], [44], [45]. Most authors assume balanced grid conditions when designing a control system for a MMC. In general there are three ways to approach the MMC control system design. The first approach is based on traditional inner current control and outer power/voltage control loop [36]-[41]. The second approach is based on total energy stored in SM capacitors of a phase leg and difference between energies in upper and lower arms [42]-[45] The third approach is based on open loop control strategy as discussed in [35], [42] and [45].

In the first approach various types of control schemes are investigated. References [36] proposes new averaging and balancing control that controls arm currents as well as reduces circulating currents. Traditional Proportional Integral and Proportional Resonant controllers are presented in [38], [39]. References [40] & [41] provide a deadbeat control approach for faster dynamic response of MMC.

The second approach of energy based control has been investigated for both open loop and closed loop conditions. The open-loop approach [45] is based on estimation of stored energy in the arms by combining the converter voltage references, measured output current and the know DC voltage. In the closed loop approach [43] a decoupled double synchronous frame current control strategy is used to control total leg energy and arm difference energy. The paper uses two rotating frames (for fundamental and 2<sup>nd</sup> harmonic current) in dq0 co-ordinates to control the total energy oscillations and energy differences.

In order to understand the basic MMC operation a simulation model is developed using a commonly applied control approach. Therefore this section focuses on developing traditional closed loop control system that has been used widely among the literature.

The control system is composed of three control loops. On the top level there is outer power control loop which has two controllers, an active power controller and a reactive power controller. The references for power controllers are defined by the target application. The 2<sup>nd</sup> level of control loop is the inner phase current control loop. The phase current controller is responsible for producing phase currents of desired amplitude (usually symmetric and sinusoidal). The current controllers are operated in synchronous frame or dq frame domain where three-phase sinusoidal variables are transformed into two-phase DC components using Park transformation. One advantage of this technique is that when these dc components are controlled by proportional-integral controllers, it assures zero steady-state error.

The references for phase current controller are derived from outer power controllers. The output of active power controller is treated as d-axis current controller reference while output of reactive power controller is treated as q-axis current controller reference. Along with the phase current controller another current controller is required, which is the circulating current controller. The circulating current controller is used for minimizing the 2<sup>nd</sup> harmonic circulating current flowing through phase legs. Outputs of phase current controller and circulating current controller are added together to form complete modulating signal.

The current controller output is called inner emf  $(e_{j\_ref})$ . Using equations (2.8) and (2.9) the upper and lower arm reference voltages are calculated, where  $u_{diff}$  is the

control voltage generated by circulating current controller. The upper and lower arm reference voltages ( $u_{pj\_ref}$  and  $u_{nj\_ref}$ ) are biased by Vdc/2, then normalized by dividing with V<sub>dc</sub> and then passed to the modulation block. The construction and design of all three controllers is discussed in the following section.

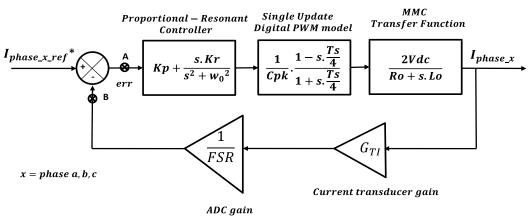

#### PHASE CURRENT CONTROLLER DESIGN:

The goal of phase current controller is to generate modulating signals that produces desired phase currents. The block diagram of a current controller to be designed is shown in Figure 2.9, where Kp, Ki are controller gains, Ts is sampling time, Vdc is DC bus voltage,  $R_0 \& L_0$  are resistance and inductance of arm inductor,  $C_{pk}$  is carrier frequency peak ( $C_{pk} = Vdc$ ), FSR is full scale range for ADC,  $G_{TI}$  is current transducer gain. For simplicity of computation FSR and  $G_{TI}$  can be approximated to 1. This makes feedback path gain =1, i.e. unity feedback.

Figure 2.9 Block diagram of phase current control loop

Using block diagram of Figure 2.9 controller gains based on desired gain and phase margins at desired crossover frequency can be calculated. The procedure for calculation of controller gains and bode plots is explained in Appendix A.1.

The closed loop transfer function of complete phase current control loop is given by equation (2.19).

$$G_{CL}(s) = \frac{0.466s^3 + 285.2s^2 + 2.38e04s}{0.0002626s^4 + 0.5178s^3 + 287.7s^2 + 2.38e04s}$$

(2.19)

The control structure of phase current controllers to be implemented is shown in Figure 2.10. The cross-coupling between d-q axis due to inductance 'Lo' is compensated using feed-forward signals. Decoupling of d-q axis makes the performance of current controller independent of synchronous frame frequency.

Figure 2.10 Control structure of phase current controllers

### ACTIVE AND REACTIVE POWER CONTROLLER DESIGN:

Figure 2.11 and Figure 2.12 shows the block diagram of active and reactive power controllers. Where *Vph* is peak phase voltage and equation (2.19) represents equivalent transfer function of current control loop. By using block diagram of Figure 2.11 and Figure 2.12 controller gains based on desired gain and phase margins at desired crossover

frequency can be calculated. The procedure for calculation of controller gains and corresponding bode plots is explained in Appendix A.2.

Figure 2.11 Block diagram of Active Power control loop

Figure 2.12 Block diagram of Reactive power control loop

The closed loop transfer function of complete power control loop is given by equation (2.20). The control structure of power controllers to be implemented is shown in Figure 2.13.

$$G_{CL}(s) = \frac{0.03812s^7 + 102.6s^6 + 1.002e5\,s^5 + 4.238e7s^4 + 7.736e9s^3 + 6.276e11s^2 + 1.87e13s}{6.896e - 8s^8 + 0.03843s^7 + 103s^6 + 1.005e5s^5 + 4.2448e7s^4 + 7.749e9s^3 + 6.282e11s^2 + 1.875e13s} \tag{2.20}$$

Figure 2.13 Control structure of power controllers

Figure 2.14 Block diagram of circulating current control loop

Figure 2.14 shows block diagram of circulating current control loop. Circulating current controller works in parallel with phase current controller. The goal of circulating current controller is to minimize the 2<sup>nd</sup> harmonic circulating current within the three phase legs of MMC as requested by its reference input. The reference is usually kept to zero in order to reduce the peak arm currents and losses caused by the circulating current.

By using block diagram of Figure 2.14 controller gains based on desired gain and phase margins at desired crossover frequency can be calculated. The procedure for calculation of controller gains and corresponding bode plots is explained in Appendix A.3. The closed loop transfer function of complete power control loop is given by equation (2.21).

$$G_{CL}(s) = \frac{0.466s^3 + 285.2s^2 + 2.38e04s}{0.0002626s^4 + 0.5178s^3 + 287.7s^2 + 2.38e04s}$$

(2.21)

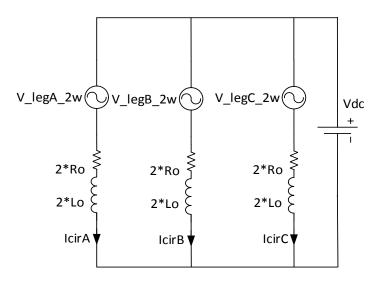

Figure 2.15 shows the control structure of the circulating current suppressing controller [10]. The circulating current of each phase is calculated by adding respective

upper and lower arm currents and then dividing by 2 according to equation (2.3). This three-phase current is then transformed into the double line frequency negative sequence rotational frame ( $i_{2fd} \& i_{2fq}$ ). The references for d and q axis controllers are zero since circulating current should not have any AC components. The controller outputs are then transformed back to three-phases using inverse park transformation  $T_{dq/acb}$ .

Figure 2.15 Control structure for circulating current controller

# 2.5 SIMULATION VERIFICATION OF MMC SYSTEM WITH DESIGNED CONTROLLERS

In order to verify the operation of PSC-PWM modulation method, conventional voltage balancing algorithm and all the controllers a simulation model was developed. Figure 2.16 shows the system connections used for MMC simulation where the MMC from Figure 2.1 is implemented. The simulation is carried out for a six-level MMC that is connected between AC grid and a DC bus. The simulation was performed in Simulink.

Table 2.1 lists circuit parameters and operating conditions used for the test MMC.

The MMC is designed for full load rated power of 60kVA.

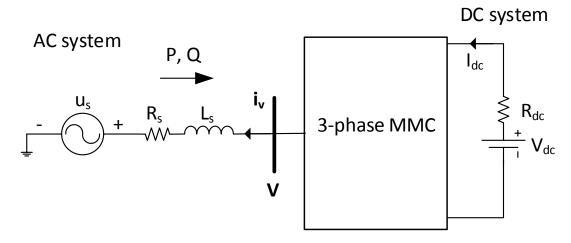

Figure 2.16 Simulation system connections between AC and DC bus

Table 2.1 Main Circuit Parameters and Operating Conditions of Simulated System

| Parameters                | Designation | Values  |

|---------------------------|-------------|---------|

| Active power              | P           | 60kW    |

| Reactive power            | Q           | 20kVar  |

| Ph-Ph RMS AC voltage      | Vg          | 208V    |

| AC system inductance      | Ls          | 0.1nH   |

| AC system Resistance      | Rs          | 0.1Ohm  |

| DC bus voltage            | Vdc         | 800V    |

| DC resistance             | Rdc         | 0.01Ohm |

| Number of SM per arm      | N           | 6       |

| SM capacitance            | Co          | 15000uF |

| Arm Inductance            | Lo          | 1mH     |

| Arm equivalent resistance | Ro          | 0.1Ohm  |

| SM capacitor voltage      | Vc          | 133.33V |

| Carrier frequency         | Fc          | 500Hz   |

| Sampling frequency        | Fs          | 3000Hz  |

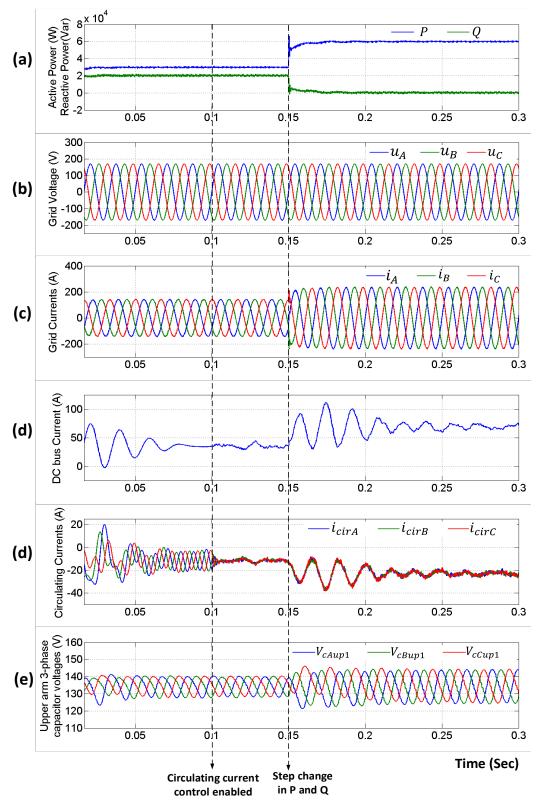

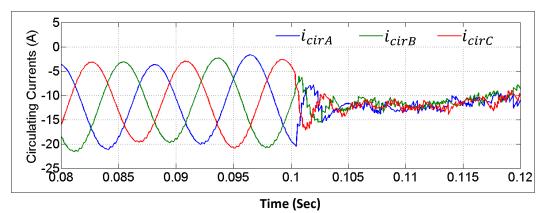

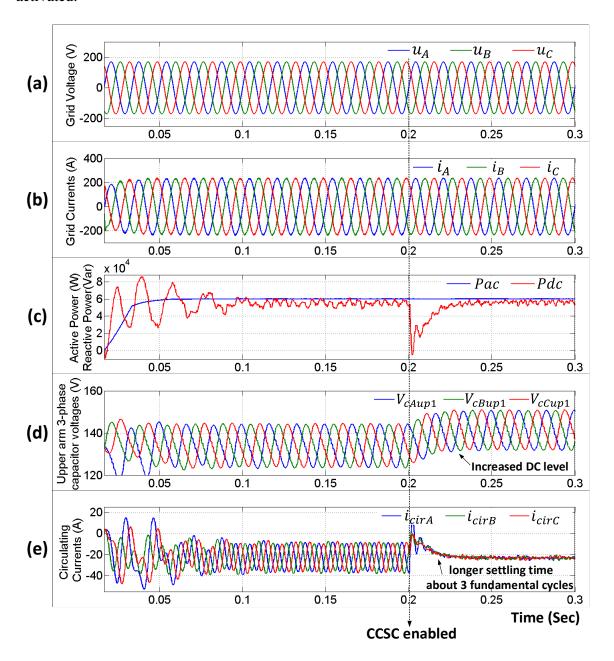

Some of the important results of simulation are shown in Figure 2.17. The simulation begins with P=30kW and Q=0Var as shown Figure 2.17 (a). The step change in active and reactive power occurs at 0.2sec with P=60kW and Q=20kVar. Both the active and reactive power reach to steady state within 0.1sec. Phase currents are sinusoidal and symmetric (Figure 2.17 (c)). Circulating currents are minimized to a small value after CCSC is enabled at 0.15sec (Figure 2.17 (e)). This validates the performance of all the controllers.

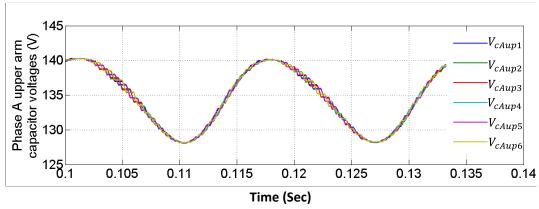

The performance of circulating current suppressing controller (CCSC) is also shown in Figure 2.18. Prior to enabling this controller the circulating current is about 12A peak to peak and after enabling the controller it minimized to about 3A peak to peak. Also it can be observed from Figure 2.17 that the circulating current controller doesn't affect the operation of other controllers and other system parameters. The performance of the conventional voltage balancing algorithm is shown in Figure 2.19. All the six capacitor voltages in one arm have very similar voltage waveform. This indicates excellence voltage balancing among all the capacitors in one arm.

Figure 2.17 Simulation results (a) Active and Reactive powers (b) Grid voltages (c) Grid currents (d) DC current (e) Circulating current (f) Upper arm three-phase capacitor voltages

Figure 2.18 Performance of circulating current controller (enabled at 0.15sec)

Figure 2.19 Performance of conventional voltage balancing method

This chapter discussed some fundamentals of modular multilevel converter and control design. Time-domain modeling of MMC, multilevel modulation schemes and conventional voltage balancing algorithm was briefly presented. Also, active/reactive power, phase current and circulating current control methods for MMC were developed using PI controllers and theoretical design was confirmed using bode plots and Nyquist criteria. The complete three-phase MMC system was tested in simulation and results were obtained that show the MMC performs acceptably under balance grid voltage conditions.

# CHAPTER 3

# MODULAR MULTILEVEL CONVERTER WITH NON-IDEAL AC SUPPLY

This chapter discusses the performance of the traditional control system for MMC under non-ideal AC supply condition. A set of fault test cases is created to observe the controller performance and its effect on various system parameters.

# 3.1 MMC PERFORMANCE UNDER NON-IDEAL GRID CONDITIONS

Various types of modulation schemes, voltage balancing algorithms, circulating current reduction techniques and harmonic minimization schemes that control the MMC under normal operating conditions have been proposed.. But the operation of a MMC under asymmetric or non-ideal grid supply voltage conditions is still under developed and needs more investigation in order to obtain the best possible performance under those conditions.

Using the MMC model described in Chapter 2, a system simulation was carried out to study the MMC's performance under asymmetric grid supply voltage conditions. In this simulation test case, grid phase-A voltage is reduced from 1.0 pu to 0.01 pu during normal steady-state operation of the converter to represent a single phase to ground fault

as shown in Figure 3.1 where term VU on the top is abbreviation for "Voltage Unbalance"

Figure 3.1 Grid voltage unbalance test-case for simulation

Using Fortescue transformation (explained in Appendix A) the symmetric component decomposition of corresponding three-phase voltages is shown in Table 3.1.

Table 3.1 Symmetric component decomposition of unbalanced grid voltages test case

| Parameter                                                            | Voltages: mag(pu)∠(deg)                                                      |

|----------------------------------------------------------------------|------------------------------------------------------------------------------|

| Grid unbalance test case                                             | $V_A = 0.01 \angle 0 deg$ $V_B = 1 \angle -120 deg$ $V_C = 1 \angle 120 deg$ |

| Positive sequence component                                          | $V^+ = 0.67 \angle 0 \text{deg}$                                             |

| Negative sequence component                                          | $V^{-} = 0.33 \angle 180 \text{deg}$                                         |

| Zero sequence component                                              | $V^0 = 0.33 \angle 180 \text{deg}$                                           |

| Voltage Unbalance (VU) 100*(Negative seq. Volt / Positive seq. Volt) | 49.25%                                                                       |

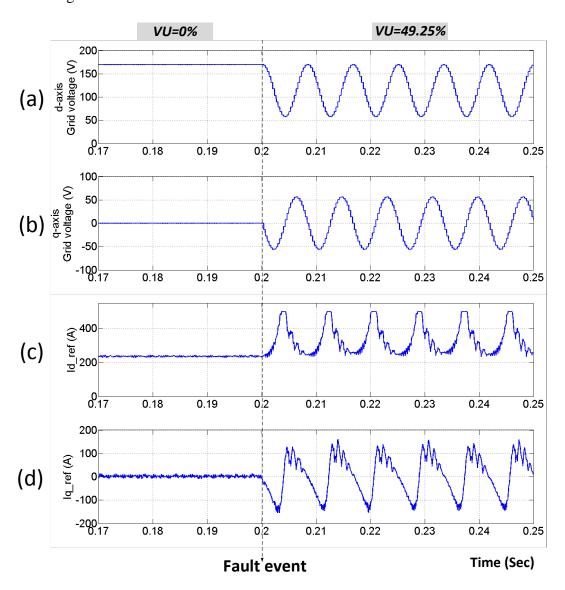

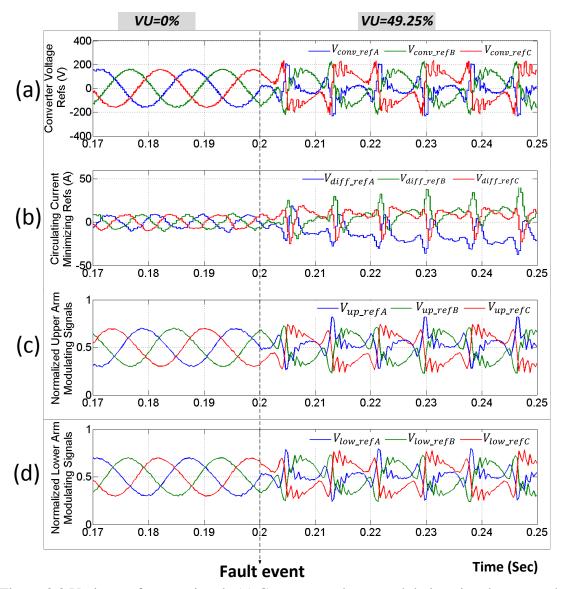

The simulation results are shown in Figure 3.2, Figure 3.3 and Figure 3.4. Figure 3.2 shows the effect of unbalance supply voltage on the corresponding d-q axis voltage and

current controller reference components. Due to unbalance voltages a 2<sup>nd</sup> harmonic sinusoidal component appears in both d and q axis grid voltage components. This affects operation of active and reactive power controllers. The power controllers then produce d-q axis current references which are also affected by the 2<sup>nd</sup> harmonic ripples. The references produced by phase current controller and circulating current controllers are shown in Figure 3.3.

Figure 3.2 Various d-q axis components (a) d-axis grid voltage (b) q-axis grid voltage (c) d-axis phase current controller reference generated by active power controller (d) q-axis phase current controller reference generated by reactive power controller

Figure 3.3 Various reference signals (a) Converter voltage modulating signal generated by phase current controllers (b) Circulating current modulating signal generated by circulating current controllers (c) Upper arm complete normalized modulating signal (d)

Lower arm complete normalized modulating signal

From Figure 3.2 and Figure 3.3 it is clear that the modulating signals are non-sinusoidal which will result in non-sinusoidal phase currents. This also affects other system parameters such as capacitor voltages, circulating currents and dc bus current. Figure 3.4 illustrates the effect of unbalance voltages on these quantities.

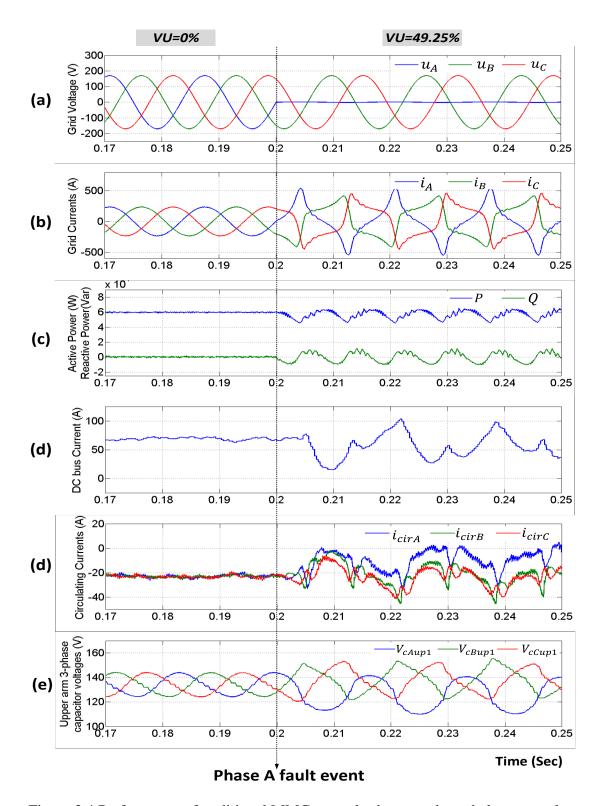

Figure 3.4 Performance of traditional MMC control scheme under unbalance supply voltage (a) Grid voltages (b) Grid currents (C) Active and Reactive powers (d) DC current (e) Circulating current (f) Upper arm three-phase capacitor voltages

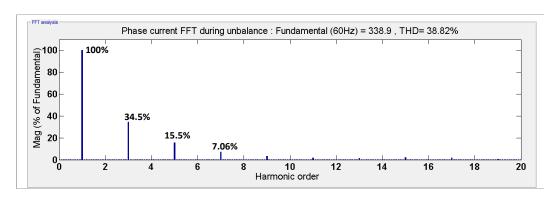

As expected from the modulating signals the phase currents are non-sinusoidal also their peak magnitude is approximately twice higher as compared to the symmetrical supply condition. A converter designed for rated power during balance supply condition may not be able to withstand such a high peak currents. Using FFT analysis the frequency components in the phase currents are obtained as shown in Figure 3.5. It can be seen that  $3^{rd}$ ,  $5^{th}$  and  $7^{th}$  harmonics are dominant in converter supply currents.

Figure 3.5 Frequency spectrum of phase currents during unbalance condition

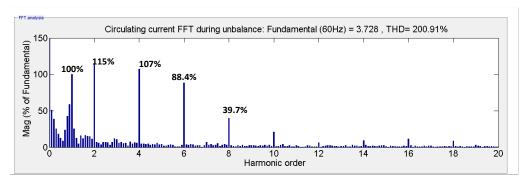

Due to the non-sinusoidal nature of phase currents the sub-module capacitors also have non-sinusoidal voltage ripple. These non-sinusoidal voltage ripples then cause non-sinusoidal circulating currents which make it impossible to minimize them using the controller shown in Figure 2.15 since the circulating current controller operates in 2<sup>nd</sup> harmonic synchronous frame. A frequency spectrum of circulating current during unbalance is shown in Figure 3.6.

Figure 3.6 Circulating current frequency spectrum during unbalance

From Figure 3.6 it is noted that due to the nature of capacitor voltage unbalance only even harmonic components are present in the circulating currents.

Active and reactive powers (Figure 3.4 (c)) have large ripples during fault. Due to the ripples in active power and harmonics in circulating currents the dc bus current also has ripples as shown in Figure 3.4 (d). This causes significant ripples in the dc power as well.

From the results discussed above it is clear that the traditional control approach fails to maintain acceptable performance of a MMC under unbalance conditions. It is therefore necessary to investigate the recent development in this area and understand what new strategies have been proposed and validated to improve MMC performance during asymmetrical supply conditions.

# 3.2 PREVIOUSLY SUGGESTED METHODS FOR MMC PERFORMANCE

# IMPROVEMENT UNDER SUPPLY ASYMMETRY

There has been some initiative taken by various researcher [46], [47], [48], [49], [50], [51], [52], [53] and [54] to address performance improvement under asymmetrical supply conditions. Reference [48], [50], [52], [53] & [54] proposes control reference calculation methods based on decomposition of symmetric components into positive, negative and zero sequence components in d-q frame of reference. All of these methods still suffer from various issues such as large fault transient in phase currents, higher steady state peak value of phase current, ripples in active and reactive powers, higher voltage ripple on sub-module capacitors etc.

Reference [49] attempts to remove dc bus voltage ripple by injecting zero sequence control reference into the modulating signal based on six arm inserted voltages but it to has ripples in active and reactive powers and higher magnitude of phase currents during fault. Reference [38] proposes stationary frame based proportional-resonant controller but has similar issues as mentioned above. Therefore, the need for further improvement in performance of MMCs under non-ideal grid supply conditions resulted in the method described in Chapter 4 which addresses the shortcomings outlined above.

# CHAPTER 4

# ADVANCED CONTROL STRATEGY FOR MODULAR MULTILEVEL CONVERTERS UNDER NON-IDEAL SUPPLY CONDITIONS

In order to properly control a MMC under the more general conditions of asymmetrical supply voltage an appropriate framework is needed. To manage the unbalanced currents in the converter under such conditions an orthogonal decomposition of the current that separates the unbalanced portion and balanced portions can be used. The following sections describe development of a new MMC control structure based on an appropriate current decomposition.

# 4.1 CURRENT'S PHYSICAL COMPONENT (CPC) POWER THEORY

The CPC theory was developed in the frequency domain by Czarnecki [46] is based on orthogonal decomposition of the current. This theory provides a physical interpretation of power phenomena in three-phase systems under unbalanced and non-sinusoidal conditions.

The theory decomposes the current into active, reactive, unbalanced and harmonic components.

$$i = i_a + i_r + i_u + i_h$$

(4.1)

where, i is defined as a vector of three phase currents  $[i_A i_B i_C]^T$  and  $i_a, i_r, i_u, i_h$ , are defined as active, reactive, unbalanced and harmonic components of that current vector respectively. In a power converter system fed with sinusoidal supply voltages, only the active power, reactive power and unbalanced power of the fundamental are concerned, and it is not necessary to decompose all the harmonics. Then, a subset of the theory, namely, the fundamental current component is expressed as follows:

$$i = i_a + i_r + i_u \tag{4.2}$$

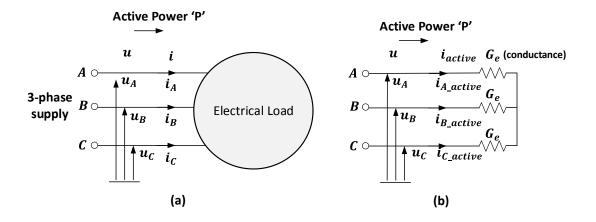

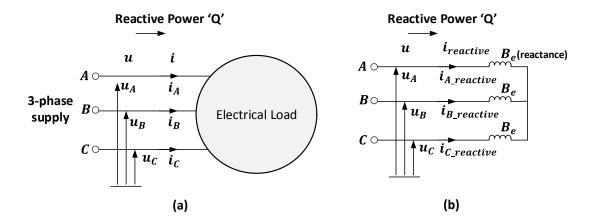

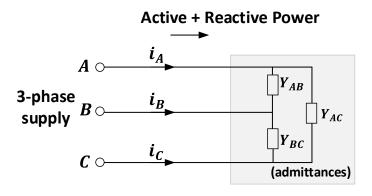

Consider Figure 4.1 (a) which shows a linear, time-invariant load supplied with a sinusoidal symmetrical voltage of positive sequence and consumes only active power. For any such system there exists an equivalent resistive and balanced load, shown in Figure 4.1 (b), which has same voltage and the same active power P as the original load. Similarly, there can be representation of a three phase system that only provides reactive power as shown in Figure 4.2 (a). The equivalent representation of such system would be an inductive and balanced load as shown in Figure 4.2 (b).

Figure 4.1 Three phase system with active power

Figure 4.2 Three-Phase system with reactive power

The case where the three-phase system has to supply both active and reactive powers can be represented by equivalent admittance load as shown in Figure 4.3.

Figure 4.3 Three-Phase system equivalent circuit with both active and reactive powers

Under balanced supply and balanced load conditions the system of Figure 4.3 only consists of active and reactive powers. But if either of the supply or load is unbalanced then along with active and reactive powers there will exist a third component called unbalanced power. These powers are directly related to active, reactive and unbalanced currents. These currents are orthogonal. For converter control purposes these current components need to be decomposed so that they can be controlled individually. In order to perform this decomposition the load is expressed in terms of two admittances the

equivalent admittance and the unbalanced admittance. The equivalent admittance is expressed as

$$Y_e = G_e + jB_e = Y_{AB} + Y_{BC} + Y_{AC}$$

(4.3)

Where,  $G_e \& B_e$  are the equivalent conductance and equivalent susceptance respectively. The unbalanced admittance is

$$A = Ae^{j\emptyset} = A\cos\emptyset + jA\sin\emptyset = (Y_{AB} + \alpha Y_{BC} + \alpha^* Y_{AC})$$

(4.4)

where,  $\alpha = e^{j120^{\circ}}$  and  $\alpha^* = e^{-j120^{\circ}}$ .

During symmetrical supply conditions there is only a positive sequence voltage component present in the system. But during asymmetrical supply conditions, the supply consists of positive, negative as well as zero sequence voltage components. In this situation a decision must be made regarding what sort of power should be consumed. Consuming power with respect to the negative sequence voltage component means injecting negative sequence current in to the grid. This is generally not feasible since many circuit breakers are designed to detect negative sequence current components and trip the breaker. Consuming power from zero sequence voltage components means injecting zero sequence current into the grid. Zero sequence power never exists with only dc value or only ripple, rather it has both dc and ripple components. Therefore the power ripple is unavoidable if zero sequence power is consumed. In addition, the zero sequence current also causes many other issues such as high neutral current, high neutral to ground voltage, low power factor, high system losses etc. Therefore the only way a good quality of power that can be consumed during unbalanced voltage is by using positive sequence voltage component.

Using the positive sequence voltage component it is possible to inject amplitude and phase symmetric positive sequence currents into the grid producing power components that are ripple free. If the phase currents are balanced then the circulating currents can also be controlled. This also would result in ripple free power on the dc side as well. Due to these reasons for the developed MMC control method presented later the decomposition of phase currents into active, reactive and unbalance components is done with respect to positive sequence supply voltage.

Having the admittances from equation (4.3) and (4.4) the three-phase active current vector can now be written as a function of positive sequence supply voltage as given by,

$$i_a = \sqrt{2}Re\left\{Ge\left[U_A^+ \ U_B^+ \ U_C^+\right]^T e^{jw_1t}\right\}$$

(4.5)

The voltages  $U_A$ ,  $U_B$  &  $U_C$  are symmetrical since they are positive sequence components, then above equation becomes,

$$[U_A^+ \ U_B^+ \ U_C^+]^T = [U^+ \ U^+ e^{-j2\pi/3} \ U^+ e^{j2\pi/3}]$$

(4.6)

Then

$$i_{a} = \begin{bmatrix} i_{Aa} \\ i_{Ba} \\ i_{Ca} \end{bmatrix} = \sqrt{2}Ge \begin{bmatrix} \mathbf{U}^{+}cos(wt) \\ \mathbf{U}^{+}cos(wt - 2\pi/3) \\ \mathbf{U}^{+}cos(wt + 2\pi/3) \end{bmatrix}$$

(4.7)

Similarly,

$$i_r = \sqrt{2}Re\left\{jBe\left[U_A^+ U_B^+ U_C^+\right]^T e^{jw_1t}\right\}$$

(4.8)

$$i_{r} = \begin{bmatrix} i_{Ar} \\ i_{Br} \\ i_{Cr} \end{bmatrix} = \sqrt{2}Be \begin{bmatrix} \mathbf{U}^{+}sin(wt) \\ \mathbf{U}^{+}sin(wt - 2\pi/3) \\ \mathbf{U}^{+}sin(wt + 2\pi/3) \end{bmatrix}$$

(4.9)

And

$$\boldsymbol{i_u} = \sqrt{2}Re\left\{A\left[\boldsymbol{U_A}^+ \ \boldsymbol{U_B}^+ \ \boldsymbol{U_C}^+\right]^T e^{jw_1t}\right\}$$

(4.10)

$$\mathbf{i}_{u} = \begin{bmatrix} i_{Au} \\ i_{Bu} \\ i_{Cu} \end{bmatrix} = \sqrt{2}A \begin{bmatrix} \mathbf{U}^{+}cos(wt + \emptyset) \\ \mathbf{U}^{+}cos(wt + \emptyset + 2\pi/3) \\ \mathbf{U}^{+}cos(wt + \emptyset - 2\pi/3) \end{bmatrix}$$

(4.11)

By extracting frequency domain components of grid voltages and phase currents (as explained in next section) active, reactive and unbalance current components present in the phase currents can be found. Then by using the above mentioned relationship between grid voltages, currents and system admittances the desired phase current references can be generated. These references can then be used to control the phase currents using proportional—resonant controllers operating in the ABC frame in order to control them individually.

# 4.1.1 RDFT BASED HARMONIC COMPONENT EXTRACTION